# First International Workshop on Bounded Model Checking

# **BMC'03**

13 July, 2003 Boulder, Colorado, USA

#### **Preface**

This binder includes the preliminary proceedings of the first international workshop on Bounded Model Checking (BMC'03) that was held on July 13th, 2003 in Boulder, Colorado. The final proceedings will be published in issue 4, Volume 89 of Electronic Notes in Theoretical Computer Science (ENTCS), together with other CAV'03 affiliated workshops.

Since its introduction in 1999, Bounded Model Checking has been adopted by most relevant companies as a complementary technique to the more traditional BDD-based unbounded symbolic model checking. Largely due to the advances in SAT technology in the last few years, it became a leading tool in detection of relatively shallow logical errors, outperforming BDD based tools in most of these cases. The large interest in this technology has created a constant stream of new ideas and improvements that make this technique more and more useful. It also led to an effort, reported in the invited talk of this workshop, to use the power of SAT solvers for standard, i.e., unbounded, model checking.

The aim of the workshop was to provide a forum for presenting new results, both theoretical and experimental, in Bounded Model Checking. This is the first workshop to concentrate on this topic, and we hope that it will be followed by similar meetings annually.

Each of the papers selected to this workshop has been reviewed and recommended by at least three (typically four) program committee members. We thank the program committee members for their effort in evaluating the articles. We also thank the organizers of the hosting conference (CAV'03), W. Hunt and F. Somenzi.

Ofer Strichman Carnegie-Mellon University Armin Biere ETH Zürich

July 2003

# **Organizers**

Ofer Strichman (Carnegie-Mellon University, USA)

Armin Biere (ETH Zürich, Switzerland)

## **Program committee**

David Basin (ETH Zürich, Switzerland) Armin Biere (ETH Zürich, Switzerland)

Per Bjesse (Synopsys, USA) Alessandro Cimatti (IRST, Italy) Raanan Fraer (Intel, Israel)

Danny Geist (IBM - HRL, Israel)

Alan Hu (Univ. of British Columbia, Canada)

James Kukula (Synopsys, USA) Ken McMillan (Cadence, USA)

Sharad Malik (Princeton Univ., USA)

Mary Sheeran (Chalmers Univ. of Technology, Sweden) Joao M. Silva (Technical Univ. of Lisbon, Portugal)

Ofer Strichman (Carnegie Mellon Univ., USA)

Toby Walsh (Univ. of York, UK) Yunshan Zhu (Synopsys, USA)

# **Program**

#### **Invited talk**

Ken McMillan

From Bounded to Unbounded Model Checking

#### Lectures

Niklas Eén, Niklas Sörensson

Temporal Induction by Incremental SAT Solving

Toni Jussila, Keijo Heljanko, Ilkka Niemelä

BMC via On-the-Fly Determinization

Parthasarathy Madhusudan, Wonhong Nam, Rajeev Alur

Symbolic Computational Techniques for Solving Games

Zurab Khasidashvili, Ziyad Hanna

SAT-based Methods for Sequential Hardware Equivalence Verification Without Synchronization

Bing Li, Fabio Somenzi

A Satisfiability-Based Approach to Abstraction Refinement in Model Checking

Gianpiero Cabodi, Alex Kondratiev, Sergio Nocco, Stefano Quer, Yosinori Watanabe

A BMC-Formulation for the Scheduling Problem in Highly Constrained Hardware Systems

# Temporal Induction by Incremental SAT Solving

Niklas Eén, Niklas Sörensson

Chalmers University of Technology, Sweden {een,nik}@cs.chalmers.se

#### Abstract

We show how a very modest modification to a typical modern SAT-solver enables it to solve a series of related SAT-instances efficiently. We apply this idea to checking safety properties by means of temporal induction, a technique strongly related to bounded model checking. We further give a more efficient way of constraining the extended induction hypothesis to so called loop-free paths. We have also performed the first comprehensive experimental evaluation of induction methods for safety-checking.

#### 1 Introduction

In recent years, SAT-based methods for hardware verification have become an important complement to traditional BDD-based model checking. Several methods have proven their usefulness on a number of industrial applications, in particular bounded model checking (BMC) [BCCZ99,BCRZ99,CFF+01]. In this paper we will focus our attention on how SAT-based verification procedures can be implemented more efficiently by a tighter integration with the underlying SAT-solver.

There are three main contributions of the paper. Firstly, we show how a number of similar SAT-instances can be solved incrementally by a very modest modification of a modern Chaff-like SAT-solver [MZ01]. The technique we propose is simpler than previous attempts [WKS01], while still obtaining a performance increase of the same magnitude. Secondly, we demonstrate the incremental technique on temporal induction [SSS00], a method of checking safety properties on finite state machines (FSM). We show the impact of the incremental approach experimentally, both for proving correctness and for finding counter-examples.

Thirdly, we refine the method of ensuring completeness for temporal induction. The standard method works by requiring all states in the induction hypothesis to be *unique*. By a simple analysis of the FSM, we are able to exclude some state-variables from the uniqueness constraints, resulting in stronger requirements. This may exponentially reduce the induction depth needed. We prove that this strengthening is sound. Additionally, we demonstrate a speed-up by adding the unique states requirement dynamically for only those pairs of states where it is needed.

The experiments we have performed with our prototype tool TIP show that many properties can be proven at speeds comparable to mature BDD-based tools such as CADENCE SMV and CMU SMV.

#### 2 Preliminaries

In this paper, we consider safety properties on finite state machines (FSM). The states of the FSM are vectors of booleans, defining the values of the state variables. We assume the FSM to have a set of legal initial states, and the safety property to be specified as a propositional formula over the state variables. By reachable state space we mean all states of the FSM reachable from the initial states. Our task is to prove that the property holds for each state in the reachable state space.

In a standard manner, we will assume the transitions of the FSM to be represented by a propositional formula  $\mathbf{T}(s, s')$ , the set of initial states by a formula  $\mathbf{I}(s)$ , and further denote the safety property by  $\mathbf{P}(s)$ . We will use  $s_n$  to denote the state variables of time step n and introduce the shorthand notation  $\mathbf{I}_n$ ,  $\mathbf{P}_n$ , and  $\mathbf{T}_n$  for  $\mathbf{I}(s_n)$ ,  $\mathbf{P}(s_n)$ , and  $\mathbf{T}(s_n, s_{n+1})$ .

#### 2.1 The SAT problem

Let Bool denote the boolean domain  $\{0,1\}$ , and  $Vars := \{x_0, x_1, x_2, \ldots\}$  be a finite set of boolean variables. A literal is a boolean variable  $x_i$  or a negated boolean variable  $\overline{x_i}$ . A clause is a set of literals, implicitly disjoined. A SAT instance is a set of clauses, implicitly conjoined. A valuation is a function  $Vars \to Bool$ . A literal  $x_i$  is said to be satisfied by a valuation if its variable is mapped to 1; a literal  $\overline{x_i}$  if its variable is mapped to 0. A clause is said to be satisfied if at least one of its literals is satisfied. A model (satisfying assignment) for a SAT instance is a valuation where all clauses are satisfied. The SAT problem is to find a model for a given set of clauses.

#### 2.2 Converting formulas to SAT

There are several ways of translating a propositional formula into clauses, in such a way that satisfiability is preserved. This is typically done by introducing auxiliary variables giving names to some or all subformulas, then generating clauses that establish a definitional relation between the introduced variables and the truth-values of their respective subformulas. Any model for

the translated problem (which contains more variables) has the property that its restriction to the original set of variables yields a model for the original formula. We assume the existence of such a translation technique and introduce the following notation:

**Definition.** By  $[\varphi]^p$  we denote a set of clauses defining  $\varphi$  such that p is the literal representing the truth-value of the whole formula. We call p the definition literal of  $\varphi$ . Further, we write  $[\varphi]$  as a short hand for  $[\varphi]^p \cup \{p\}$ .

For example  $[x \wedge y]^p$  may be translated into the clauses  $\{ \{\overline{p}, x\}, \{\overline{p}, y\}, \{p, \overline{x}, \overline{y}\} \}$ .

#### 2.3 Temporal Induction

This section briefly summarizes the verification technique temporal induction presented in [SSS00]. The word "temporal" suggests that the induction is carried out over the time steps of the FSM. Like a standard induction proof, a temporal induction proof consists of two parts: the base-case and the induction-step. In its simplest form, the base-case states that the property should hold in the initial states; and the induction-step states that the property should be preserved by the transitions of the FSM. Expressing the two parts of the induction proof as SAT-problems is straight-forward—still, the resulting method is already an interesting complement to BDD-based verification methods, especially for systems where the transition relation has no succinct BDD-representation. However, the method is not complete, since the induction-step might not be provable even though the property is true.

To make the method complete, the induction-step is strengthened in two ways. Firstly, the property is assumed to hold for a path of n successive states, rather than just one. This means that a longer base-case must be proven. Secondly, the states of the path are assumed to be unique. It follows immediately from finiteness that the second strengthening makes the method complete in the sense that there is always a length for which the induction-step is provable. Soundness is treated in detail in section 4. Let us formalize the strengthened induction by defining the following formulas:

$$egin{array}{lll} \mathbf{Base}_n &:=& \mathbf{I}_0 \ \land \ \left( (\mathbf{P}_0 \land \mathbf{T}_0) \ \land \ldots \land \ (\mathbf{P}_{n-1} \land \mathbf{T}_{n-1})

ight) \ \land \ \overline{\mathbf{P}_n} \ \ \mathbf{Step}_n &:=& \left( (\mathbf{P}_0 \land \mathbf{T}_0) \ \land \ldots \land \ (\mathbf{P}_n \land \mathbf{T}_n)

ight) \ \land \ \overline{\mathbf{P}_{n+1}} \ \ \mathbf{Unique}_n &:=& \bigwedge_{i \leq j \leq n} (s_i

eq s_{j+1}) \ = \bigwedge_{i \leq j \leq n} \bigvee_k \lnot (s_{i,k} \leftrightarrow s_{j,k}) \ \end{array}$$

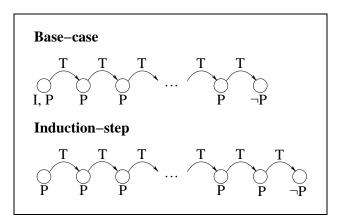

An interpretation of these formulas is depicted in Fig. 1. Note that when proving correctness we show that the formulas are *unsatisfiable*. In the basecase we assume that all shorter base-cases have been proved already, and add

<sup>&</sup>lt;sup>1</sup> The authors use only the word "induction" in this presentation, but have later adopted the term "temporal induction" and used it in other contexts.

Fig. 1. If the n-th base-case is unsatisfiable, it should be read as "There exists no n-step path to a state violating the property, assuming the property holds the first n-1 steps." If the n-th induction-step is unsatisfiable, it should be read as "Following an n-step trace where the property holds, there exists no next state where it fails".

the property to each state as this tends to make the resulting SAT-problem easier. With these definitions, we can now state an algorithm that intertwines looking for bugs of longer and longer lengths, and trying to prove the property by deeper and deeper induction-steps:

#### Algorithm 1. "Temporal Induction".

```

for n \in 0..\infty do

if (satisfiable([\mathbf{Base}_n]))

return PROPERTY FAILS

if (\neg satisfiable([\mathbf{Step}_n] \cup [\mathbf{Unique}_n]))

return PROPERTY HOLDS

```

Variations of this algorithm are also meaningful. For instance, checking only the base-case gives a pure bug-hunting algorithm, which delivers counter-examples more quickly. By altering the formula of the base-case slightly, it is possible to start at a higher n and taking bigger leaps than 1. Checking every size of n may be unnecessarily costly. If the bug or proof is deep, taking bigger leaps means solving fewer SAT-problems. However, if there is a bug, Algorithm 1 (as stated) will always find a shortest counter-example. This may be important. In the remainder of the article, we will show how the cost of incrementing n by only 1 can be greatly reduced by solving the SAT-problems incrementally.

#### 3 Incremental SAT

A typical stand-alone SAT-solver accepts a problem instance as input, solves it, and outputs a model or an "Unsatisfiable" statement as result. This can be inadequate if you wish to solve many similar SAT-instances. The most obvious overhead is re-parsing the (almost) same clause set over and over again. But more importantly, the same, often expensive, inferences may be carried out over and over again. Equipping the SAT-solver with an interface that

allows the next SAT-instance to be specified incrementally from the current (solved) instance will certainly remove the parsing problem, but may reduce the number of inferences too.

We focus on the type of solver introduced by [MS99], based on conflict analysis and clause recording. Such a solver implements a DPLL-style backtracking search procedure [DLL62]. The idea behind augmenting the basic procedure with conflict analysis is that for every conflict detected during the search, some effort is spent on finding a reason for the conflict that can be encoded as a clause and added to the clause set. The recorded clauses will serve as a cache for the same type of conflicts in later parts of the search-space. For example, if assuming x and y to be true led to a conflict, the clause  $\{\overline{x}, \overline{y}\}$  may be recorded. Assuming either x or y to be true in some later part of the search-tree, will immediately give the implied value to the other variable, avoiding repetition of the possibly lengthy derivation. The effectiveness of this idea has been empirically established by many authors. A motivation for incremental SAT is that the recorded clauses may not only be useful in later parts of the search-tree of the same SAT-instance, but also in a later similar SAT-instance.

To describe the different design issues encountered when implementing an incremental SAT-system, we adopt an object-oriented view, using a solver object which stores the problem clauses (the current SAT-instance) as well as the learnt clauses (the recorded clauses). The solver has methods for modifying and solving the current SAT-instance. The simplest imaginable interface would contain the following methods:

```

addClause (Clause c) — will add a clause to the clause database.

- will solve the current instance.

```

Using this interface, the user is allowed to add clauses until he has specified the first SAT-problem. He can then use *solve* to check if the problem is satisfiable or not. If it is, he may add more clauses to constrain the problem further and re-run *solve*. This procedure can be repeated until all SAT instances of interest have been solved. Typically the last instance is unsatisfiable, from which point no extension can be satisfiable.

This approach to incremental SAT, introduced in [Hok93], is limited as the user can never remove anything added. Many interesting incremental SAT-problems requires some form of clause removal. Therefore [WKS01] suggested the following interface to the solver:

```

addClause (Clause c)

removeClause (Clause c)

solve

(Clause c)

- will remove an existing clause from the clause database.

```

This includes SAT-solvers such as: GRASP, SATO, ZCHAFF, LIMMAT, BERKMIN, and the authors' own solvers SATNIK and SATZOO.

By this interface, any set of related problems can be solved incrementally. However, the ability to remove clauses clashes with conflict clause recording. The conflict analysis is guaranteed to produce clauses that are implied by the problem clause set; thus adding these clauses can never cause unsoundness. But removing problem clauses may suddenly render recorded clauses invalid. A detailed dependency analysis must therefore be carried out to remove the invalid clauses, which in turn may require extra book-keeping during the actual solving process. For a longer treatment of this approach see [WKS01].

In contrast, we propose the following interface which only enables the removal of unit clauses. The motivation is that it is *very* simple to implement (5 lines of code in our solver), while being expressive enough to encompass several interesting incremental SAT-problems not expressible by the original interface:

```

addClause (Clause c)

solve (list⟨Literal⟩ assumptions)

```

The extra list of literals passed to *solve* should be viewed as unit clauses to be added during this particular solving, then removed upon return from the solver. The reason that this approach is simpler is that *all* learned clauses are safe to keep, and thus no extra book-keeping is needed. To see why it is safe, note that the extra unit clauses can be seen (and implemented) as internal assumptions by the search procedure, and that it is an inherent property of conflict clauses that they are independent of the assumptions under which they occur. <sup>3</sup>

#### 4 Incremental Induction

In section 2.3 we saw a straight-forward algorithm for proving or disproving safety properties by induction. We break this algorithm into two parts, the base-case ("bug-finder") and the induction-step ("upper-bound prover"), and show how they can be implemented incrementally using the SAT-interface of section 3.

<sup>&</sup>lt;sup>3</sup> In fact, the more general interface can be simulated to a large extent. By inserting the clause  $\{x\} \cup C$ , and passing  $\overline{x}$  as an assumption literal, we achieve the same effect as inserting C. Asserting x to be true afterwards will make the clause true forever, and it will be removed from the clause database by the top-level simplification procedure of the solver.

#### Algorithm 2 "Extending base". Algorithm 3 "Extending step".

```

addClauses([\overline{\mathbf{P}_0}])

addClauses([\mathbf{I}_0])

for n \in 0..\infty do

for n \in -1..-\infty do

addClauses([\mathbf{P}_n]^{p_n})

solve(\{\})

solve(\{\overline{p_n}\})

if (Unsatisfiable)

if (Satisfiable)

return IND. STEP HOLDS

return PROPERTY FAILS

addClauses([\mathbf{T}_n])

addClause(\{p_n\})

addClauses([\mathbf{P}_n])

addClauses([\mathbf{T}_n])

for i \in 0..n+1 do

addClauses([s_i \neq s_n])

```

A first observation on these algorithms is that they build the trace of states related by the transition relation in different directions (n is decremented in the step). Growing the trace forwards in the base-case allows us to keep the often strong formula  $\mathbf{I}_0$  fixed in the SAT-solver. Building the trace in the opposite direction would force us to put the initial state constraints as an assumption literal to "solve", which will have the undesirable effect of making any recorded conflict clause depending on the initial state ineffective in successive iterations. Similarly in the step, growing the trace backwards makes it unnecessary to use any assumption literal at all, which again promotes reuse of recorded clauses between iterations.

Different top-level strategies for how to combine the two algorithms to a safety-checking procedure are possible. To emulate *Algorithm 1* of section 2.3, the algorithms could be run in parallel, each with its own solver instance. As soon as the induction-step succeeds for a particular length, an unsatisfiable base-case of that length will constitute a proof of the safety property. However, it is also possible to mix the two algorithms into one. We will then have to break the natural direction of building the trace for either the base-case or the induction-step. We arbitrarily chose to sacrifice the induction-step.

#### Algorithm 4 "Zig-zag".

```

-z is the definition literal for \mathbf{I}_0

addClauses([\mathbf{I}_0]^z)

for n \in 0..\infty do

addClauses([\mathbf{P}_n]^{p_n})

-p_n is the definition literal for \mathbf{P}_n

- step: do not include I_0

solve(\{\overline{p_n}\})

if (Unsatisfiable)

-\mathbf{P}_n must hold!

return PROPERTY HOLDS

solve(\{z,\overline{p_n}\})

- base-case: include \mathbf{I}_0

if (Satisfiable)

- counter-example found!

return PROPERTY FAILS

- assert \mathbf{P}_n from now on

addClause(\{p_n\})

addClauses([\mathbf{T}_n])

- assert transition from s_n to s_{n+1}

for i \in 0..n-1 do

- add uniqueness constraints

addClauses([\boldsymbol{s_i} \neq \boldsymbol{s_n}])

```

The reason for stating this algorithm is partly to show that there is many possible ways of encoding the safety-checking procedure incrementally. With

this algorithm, the SAT-solver is allowed to share conflict clauses between the base-case and the induction-step, which may be beneficial. We include the algorithm in our benchmark section.

#### 4.1 Discussion

We will now try to draw a map over possible induction based safety-checking algorithms. Let us use the term *bad state* for a state were the safety property does not hold. It is generally observed that checking safety properties is symmetric with respect to the initial states and the bad states. Everything presented up to this point could have been carried out backwards, with the roles of initial states and bad states exchanged, and the transition relation inverted. We are going to adopt this symmetrical view from now on.

In this view, we regard the induction-step as a method of finding an upper bound on the length of a shortest counter-example, and the base-case as a way of producing the counter-example. Now, what must a shortest counter-example look like? It has to start in an initial state, it has to end up in a bad state, and the states in between must not be either initial or bad (otherwise it could not be a shortest counter-example). Using  $\bf B$  (bad) for  $\bf \overline{P}$  we can view the set of possible shortest counter-examples pictorially:

Each line depicting a (shortest) counter-example corresponds to a conjunction of constraints ( $\mathbf{I}_0 \wedge \mathbf{T}_0 \wedge \overline{\mathbf{B}}_1 \wedge \overline{\mathbf{I}}_1 \wedge \mathbf{T}_1 \wedge \ldots$ ). There is a lot of sharing between the counter-examples of different lengths, and indeed if we remove either the initial  $\mathbf{I}$  or the final  $\mathbf{B}$  from the *n*-th counter example, i.e.:

$$(1) \qquad \overline{\mathbf{B}} \stackrel{\mathbf{T}}{\frown} \overline{\mathbf{I}} \overline{\mathbf{B}} \stackrel{\mathbf{T}}{\frown} \dots \stackrel{\mathbf{T}}{\frown} \overline{\mathbf{I}} \overline{\mathbf{B}} \stackrel{\mathbf{T}}{\frown} \overline{\mathbf{I}} \mathbf{B}$$

$$or \qquad (2) \qquad \overline{\mathbf{I}} \overline{\mathbf{B}} \stackrel{\mathbf{T}}{\frown} \overline{\mathbf{I}} \overline{\mathbf{B}} \stackrel{\mathbf{T}}{\frown} \dots \stackrel{\mathbf{T}}{\frown} \overline{\mathbf{I}} \overline{\mathbf{B}} \stackrel{\mathbf{T}}{\frown} \overline{\mathbf{I}}$$

then any counter-example of length n or longer will include all the constraints of (1) and (2). This means that if either the constraints of (1) or (2), or any subset of these, yields an unsatisfiable problem, then so will all possible shortest counter-examples of longer lengths. Thus we have found an upper bound on the shortest counter-example.

The picture above does not contain all constraints derivable from the fact

that we are considering a *shortest* counter-example. We can further conclude:

- 1. Between no two states is there a shorter path.

- or weaker 2. Between no two non-neighbors is there a transition (and the last state is unique).

- or weaker 3. No two states are the same.

Any of these facts can be used when proving an upper bound. As long as we keep adding constraints that must be fulfilled by shortest counter-examples, any contradiction reached means we have established an upper bound. The reason for stating weaker versions of the shortest-path requirement is that these versions can be implemented more efficiently. Furthermore, we have already noted that the third condition is enough to make the procedure complete. In the next section we describe how the implementation of this condition can be improved.

Taking this subset-of-counter-example view, the induction-step we have used in our algorithms can now be viewed as selecting the subset of (1) not containing any  $\overline{\bf I}$ :s but including the uniqueness constraints dictated by condition 3. <sup>4</sup> Through experiments we found that this choice worked well in practice.

#### 4.2 Finding a counter-example

If the user knows or has reason to believe that the property is false, he may want to run just the base-case to quickly produce a counter-example. In this case, it is less clear if any extra constraints should be added to the trace. In Algorithm 1 and 2 we chose to add **P**. More constraints mean more clauses in the solver, which leads to slower propagation, but also to a smaller search-tree. Which of the two effects is predominant in a particular case is hard to judge. In general, adding weak constraints is seldom a good idea.

Present BMC tools can optionally produce a SAT-problem stating that the property fails among the first n steps rather than after exactly n steps. Care must be taken before adding extra constraints to such formulations. For instance, one can no longer require the states to be unique. One must also assume (or modify) the transition relation to always have a next state; or risk getting an unsatisfiable problem due to deadlock, even in the presence of a bug. A comparison between this "one-shot" method and the incremental base-case is included in our experiments.

#### 4.3 Improving the Unique States Requirement

The uniqueness constraints described in section 2.3 and used in Algorithm 1,  $\beta$  and  $\beta$  require each pair of states to be different. These requirements are

<sup>&</sup>lt;sup>4</sup> The recurrence diameter introduced in [BCCZ99] can similarly be viewed as the subset containing only the T:s together with uniqueness constraints.

statically added, and their number will grow quadratically in the length of the induction-step. For problems requiring high induction length, there is a risk of adding numerous possibly superfluous constraints that will tax the SAT-solver heavily. We propose a dynamic approach where the models returned by the solver in the induction-step are examined, and only if two states are actually equal, a constraint stating that they should be different is added. The solver must then be run again, which may possibly cost more than adding superfluous constraints, but hopefully the incrementality of the approach means that any re-run is very quick. We verified experimentally that the method indeed seems to perform better in general.

A question that has not been treated sufficiently in earlier presentations on induction is what variables should be included in the uniqueness constraints. It is not unusual to describe the FSM in the form of a sequential circuit. The standard interpretation of a circuit is to consider both the latches (the state holding elements) and the inputs as state variables of the FSM. However, it is fairly clear that there is no need to include inputs in the uniqueness constraints. If two states are equal except for the inputs, whatever value the inputs assume in the second state, they could have assumed in the first. It is therefore safe to require only the latch-variables do be different—a much stronger condition. In fact, this is often what is implemented [CS00]. Note that failing to remove the superfluous state variables from the uniqueness constraints gives an ineffective induction algorithm, as each extra state variable has the potential of doubling the depth needed to prove the step.

If on the other hand the FSM is given as two propositional formulas **I** and **T** it is less clear what variables can be excluded. We propose the following solution:

- 1. Include only variables occurring both in the current and the next state of the transition relation.

- 2. Do not add uniqueness constraints including the first or the last state of the trace.

We refer to uniqueness constraints over this reduced set of state variables as strong uniqueness.

#### 4.4 Correctness

We will now prove that temporal induction with strong uniqueness is sound. Recall that the induction-step can be strengthened by anything that holds for a shortest counter-example. It then suffices to show that a counter-example that is not strongly unique cannot be shortest. Let us introduce the following notation:

The result of parsing an SMV file often leaves you with just this.

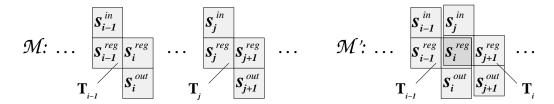

Fig. 2. The picture shows the contraction of the counter-example  $\mathcal{M}$  to  $\mathcal{M}'$ . The state variables constrained by the transition relations at the point of "gluing" are printed in the boxes; the remaining trace is represented by the "...".

$$egin{array}{lll} oldsymbol{s_i}^{left} &:= & vars(\mathbf{T}_i) \cap oldsymbol{s_i} & oldsymbol{s_i}^{in} &:= & oldsymbol{s_i}^{left} \setminus oldsymbol{s_i}^{right} \ oldsymbol{s_i}^{out} &:= & oldsymbol{s_i}^{right} \setminus oldsymbol{s_i}^{left} \ oldsymbol{s_i}^{reg} &:= & oldsymbol{s_i}^{left} \cap oldsymbol{s_i}^{right} \end{array}$$

Let  $\mathcal{M}$  be the model of a formula encoding a counter-example of depth n:

$$\mathcal{M} \models \mathbf{I}_0 \wedge \mathbf{T}_0 \wedge \mathbf{T}_1 \wedge \ldots \wedge \mathbf{T}_{n-1} \wedge \mathbf{B}_n.$$

We now show by construction that if  $\mathcal{M} \models (s_i^{reg} = s_j^{reg})$  for some 0 < i < j < n ( $\mathcal{M}$  is not strongly unique) then there is a shorter counter-example. Define  $\mathcal{M}'$  over  $\{s_0, \ldots, s_{n-(j-i)}\}$  as follows:

$$\mathcal{M}'(s_k) = \mathcal{M}(s_k)$$

,  $k < i$

$\mathcal{M}'(s_k) = \mathcal{M}(s_{k+(j-i)})$ ,  $k > i$

$\mathcal{M}'(s_i^{in}) = \mathcal{M}(s_j^{in})$

$\mathcal{M}'(s_i^{out}) = \mathcal{M}(s_i^{out})$

$\mathcal{M}'(s_i^{reg}) = \mathcal{M}(s_i^{reg})$

$\mathcal{M}'$  now constitutes a counter-example of depth n-(j-i). We have contracted the counter-example by simply removing all states between i and j (depicted in Fig. 2). The only potential problem lies in the "gluing" of the head and the tail at state i. However, the only constraints containing  $s_i$  are  $\mathbf{T}_{i-1}$  and  $\mathbf{T}_i$ . But  $\mathbf{T}_{i-1}$  does not contain any variables from  $s_i^{in}$ , so letting  $\mathcal{M}(s_i^{in}) \neq \mathcal{M}'(s_i^{in})$  cannot make  $\mathbf{T}_{i-1}$  false in  $\mathcal{M}'$ . Similarly for  $\mathbf{T}_i$  which does not contain any variables from  $s_i^{out}$ . Finally  $\mathcal{M}(s_i^{reg}) = \mathcal{M}(s_j^{reg})$ , so indeed  $\mathcal{M}'$  must be a model for the constraints  $\mathbf{T}_{i-1}$  and  $\mathbf{T}_i$ .

The proof can easily be extended to establish that the exclusion of the first and the last state is superfluous if all variables of **I** occur in the next state of **T** and all variables of **B** occur in the current state of **T**.

### 5 Experimental Results

The ideas presented in this paper were implemented in the prototype tool TIP<sup>6</sup> which was integrated with the SAT-solver SATZOO. All benchmarks were performed on a 2 GHz Pentium 4 with 512 MB of memory running Linux. We set the time-out for all launches to 10 minutes, and the memory limit to 400 MB. The benchmarks were collected from several sources. In the tables, each benchmark name is tagged with the source of the problem:

texas – The Texas 97 benchmarks from Berkeley University.

eijk – ISCAS'89 sequential equivalence checking from [Eijk98].

irst – Problems from the Model Checking Group at IRST.

All problems were converted to flat SMV-format with only boolean variables and no sub-modules. For each problem, the safety properties were extracted. In this process, CTL formulas "EF" were changed into "AG¬" and all fairness constraints were removed. Different properties for the same system are indicated by a subscript after the system name.

Counting each property as a separate instance, a total of 185 problem instances were collected. As our first experiment, we ran TIP, CADENCE SMV, CMU SMV, and NuSMV on each of these instances. All tools were run with a default set of options, providing no problem specific variable ordering:

```

Tip filename

CadSMV filename

CmuSMV -reorder filename

NuSMV -AG -dynamic -coi filename

```

Instances solved in less than 1 second by all tools were considered trivial and removed, leaving 158 instances.

#### 5.1 Comparison with BDD-tools

The result of the comparative experiment is presented in Table 1. The default strategy of TIP runs the base-case and the induction-step presented in Algorithm 2 and 3 in parallel, each with its own solver instance. The two algorithms are given equal amount of CPU time, until the point where either the base-case fails, and a counter-example is found, or the induction-step is

<sup>&</sup>lt;sup>6</sup> The tool TIP, the SAT-solver SATZOO and all benchmarks used in this article can be downloaded from  $http://www.cs.chalmers.se/\sim een/$

proven, and the remaining base-cases (if any) are proved with 100% CPU.

The purpose of the experiment was to relate the performance of induction to industrially applied methods, and to show the (lack of) correlation between hardness for BDD-based methods and hardness for induction-based methods. TIP was able to solve 6 instances where BDD-based verification failed, showing that induction may be a valuable complementary method. <sup>7</sup>

#### 5.2 Effect of incrementality

The second experiment we performed was a comparison of Algorithm 2 and 3 using the incremental interface of SATZOO and using SATZOO as an external solver. In this experiment, we used only problem instances where the property held. The result is presented in Table 2.

The experiment establishes a substantial speed-up by the incremental approach. Unsurprisingly, the gain was larger for instances where a long induction-step was needed to prove the property.

From the table we can also see that the induction-step usually takes longer to prove than the base-case. We observed the same behavior for instances where the property failed (although not presented here). This is the reason the default strategy of TIP does not increase the lengths of the step and base evenly, but instead devotes the same amount of CPU to each. Otherwise, bugs may not be found due to hard (and futile) induction-steps.

#### 5.3 One solver instance or two

The third experiment compared Algorithm 4 ("Zig-Zag") using one solver instance to running the induction-step and the base-case in separate solver instances. ("Dual"). In this experiment, the step and the base were incremented evenly so that both methods would solve only the minimal number of SAT-instances. We also include the standard implementation of (complete) induction as presented in [SSS00]. The results are also in Table 2.

The experiment suggests that separate solver instances for the base and the step is favorable. From the table we can also see that the incremental implementation of induction clearly outperforms the standard implementation.

#### 5.4 BMC Comparison

In the fourth experiment, we compared incremental search for counter-example to the "one-shot" approach described in section 4.1. The result is presented in *Table 3*. The experiment shows that often you must know the exact length of a shortest counter-example for the one-shot method to be advantageous.

<sup>&</sup>lt;sup>7</sup> These problems were all "TCAS II" problems from the NUSMV distribution, originally used in "Model Checking Large Software Specifications" [CAB98].

| Tool        | 201.04 | Alone in solving |

|-------------|--------|------------------|

| CADENCE SMV | 131    | 5                |

| TIP         | 92     | 6                |

| CMU-SMV     | 90     | 0                |

| NUSMV       | 73     | 0                |

Table 1. Tool comparison. The left column shows the total number of solved instances within 10 minutes. The right column show how many of these instances no other tool could solve. CADENCE SMV excelled by proving 22 instances that neither of the two other SMVs could prove, and 39 more instances than TIP. Still only 5 instances were unique, as TIP solved many of the problems where NUSMV and CMU-SMV failed, plus 6 that CADENCE SMV did not solve.

| Name                               | Len | $Step^{inc}$ | $\mathrm{Step}^{ext}$ | Base $^{inc}$ | $\mathrm{Base}^{ext}$ | Dual   | ZigZag | $\operatorname{StdInd}$ |

|------------------------------------|-----|--------------|-----------------------|---------------|-----------------------|--------|--------|-------------------------|

| cmu:periodic                       | 97  | 70.7         | [>600]                | 10.7          | 141.8                 | 80.9   | [>600] | [>600]                  |

| eijk:S $208c$                      | 259 | 448.0        | [>600]                | [>600]        | [>600]                | [>600] | [>600] | [>600]                  |

| eijk:S $208o$                      | 258 | 483.2        | [>600]                | [>600]        | [>600]                | [>600] | 564.2  | [>600]                  |

| eijk:S $208$                       | 259 | 436.7        | [>600]                | [>600]        | [>600]                | [>600] | 503.7  | [>600]                  |

| eijk:S298                          | 59  | 27.7         | [>600]                | 34.9          | 96.2                  | 62.9   | 316.1  | [>600]                  |

| eijk:S $510$                       | 11  | 5.2          | 8.0                   | 0.5           | 0.9                   | 5.9    | 7.4    | 10.1                    |

| eijk:S820                          | 12  | 6.1          | 22.9                  | 6.4           | 12.5                  | 12.6   | 20.2   | 30.1                    |

| eijk:S832                          | 12  | 7.6          | 28.2                  | 5.8           | 12.9                  | 13.4   | 25.1   | 35.2                    |

| eijk:S $953$                       | 8   | 1.7          | 4.2                   | 0.1           | 0.2                   | 1.9    | 4.2    | 4.4                     |

| $ken:oop_1$                        | 30  | 39.4         | [>600]                | 0.3           | 7.4                   | 39.9   | 492.0  | 254.0                   |

| nusmv: guidance <sub>1</sub>       | 11  | 2.8          | 10.2                  | 0.8           | 3.4                   | 3.5    | 3.9    | 11.1                    |

| nusmv: guidance <sub>7</sub>       | 28  | 120.3        | [>600]                | 315.0         | [>600]                | 438.9  | [>600] | [>600]                  |

| $nusmv$ :tcas $_2$                 | 7   | 1.3          | 3.1                   | 0.2           | 0.3                   | 1.5    | 1.9    | 4.3                     |

| $nusmv$ :tcas $_3$                 | 6   | 1.3          | 3.3                   | 0.0           | 0.1                   | 1.3    | 1.8    | 3.2                     |

| texas:parsesys <sub>2</sub>        | 4   | 12.2         | 13.5                  | 0.2           | 0.2                   | 14.7   | 12.5   | 7.8                     |

| ${\it vis}$ : ${ m prodcell_{12}}$ | 30  | 256.6        | [>600]                | 112.8         | 445.5                 | 367.3  | [>600] | [>600]                  |

| ${\it vis}$ :prodcell $_{13}$      | 9   | 4.6          | 12.4                  | 0.1           | 0.6                   | 4.8    | 3.7    | 14.7                    |

| ${\it vis}$ :prodcell $_{14}$      | 17  | 31.3         | 185.1                 | 7.3           | 14.2                  | 38.7   | 52.3   | 219.9                   |

| ${\it vis}$ : ${ m prodcell_{15}}$ | 24  | 109.3        | [>600]                | 23.0          | 80.1                  | 132.4  | 216.7  | [>600]                  |

| ${\it vis}$ :prodcell $_{16}$      | 6   | 2.1          | 4.1                   | 0.0           | 0.1                   | 2.1    | 1.2    | 4.7                     |

| ${\it vis}$ :prodcell $_{17}$      | 28  | 211.3        | [>600]                | 52.4          | 277.5                 | 265.0  | [>600] | [>600]                  |

| ${\it vis}$ :prodcell $_{18}$      | 14  | 21.4         | 117.9                 | 0.4           | 3.2                   | 21.8   | 28.6   | 128.9                   |

| ${\it vis}$ :prodcell $_{19}$      | 23  | 61.6         | 457.0                 | 23.4          | 86.0                  | 85.0   | 178.5  | [>600]                  |

| $\mathit{vis}$ :prodcell $_{24}$   | 38  | 391.9        | [>600]                | [>600]        | [>600]                | [>600] | [>600] | [>600]                  |

Table 2. Experimental results for the effect of incremental SAT vs. external SAT. All times are in seconds. The experiment includes all instances where the property was proved to hold in in the first experiment. Launches where all methods took less than 3 seconds have been left out. "Dual" stands for running one iteration of Alg.2 and Alg.3 interchangeably; "ZigZag" refers to Alg.4; "StdInd" stands for standard induction with all uniqueness constraints statically added and using an external SAT-solver.

| Name                                                                                                                                                                                                  | Length                                | Incremental<br>BMC                              | Perfect<br>Guess                                | 25%-off<br>Guess                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------|-------------------------------------------------|---------------------------------------------------|

| nusmv:tcas <sub>1</sub><br>nusmv:tcas <sub>4</sub><br>nusmv:tcas <sub>5</sub><br>nusmv:tcas <sub>6</sub><br>texas:parsesys <sub>1</sub><br>texas:parsesys <sub>3</sub><br>texas:two-proc <sub>2</sub> | 11<br>15<br>24<br>17<br>10<br>9<br>16 | 3.6<br>9.7<br>48.7<br>13.6<br>9.3<br>3.3<br>4.7 | 3.7<br>9.7<br>40.1<br>13.5<br>0.8<br>0.7<br>1.0 | 5.0<br>18.2<br>125.2<br>38.2<br>1.1<br>0.9<br>2.9 |

| $texas$ : two-proc $_4$<br>vis: eisenberg                                                                                                                                                             | $\frac{20}{20}$                       | $20.9 \\ 20.7$                                  | 1.8<br>18.1                                     | 9.1 $79.1$                                        |

Table 3. Experimental result for incremental BMC vs. SAT-instances of fixed length. All times are in seconds. "Perfect Guess" means the SAT-instance encode "there is a bug of length  $\leq k$ " where k is the length of the shortest counter-example. "25%-off" means k is multiplied by 1.25. Launches where all methods took less than 3 seconds have been left out.

| Name                    | Len | $\mathrm{Time}^d$ | $\mathrm{Time}^s$ | $\operatorname{Ban}^d$ | $\mathrm{Ban}^s$ | $\mathrm{Clau}^d$ | $\mathrm{Clau}^s$ | $\mathrm{Conf}^d$ | $\mathrm{Conf}^s$ |

|-------------------------|-----|-------------------|-------------------|------------------------|------------------|-------------------|-------------------|-------------------|-------------------|

| cmu:periodic            | 97  | 70.7              | 120.4             | 0                      | 4656             | 455k              | 908k              | $15\mathrm{k}$    | 14k               |

| eijk:S $208$            | 259 | 436.7             | [>600]            | 258                    | [>20000]         | 186k              | -                 | 76k               | -                 |

| eijk:S298               | 59  | 27.7              | 66.6              | 114                    | 1653             | 69k               | 296k              | 24k               | 25k               |

| $ken:oop_1$             | 30  | 39.4              | 50.4              | 113                    | 406              | 67k               | 101k              | 32k               | 30k               |

| nusmv:guidance7         | 28  | 120.3             | 66.9              | 0                      | 378              | 151k              | 276k              | 56k               | 28k               |

| $vis$ :prodcell $_{12}$ | 30  | 256.6             | 252.7             | 0                      | 406              | 346k              | 439k              | 48k               | 43k               |

| $vis$ :prodcell $_{14}$ | 17  | 31.3              | 41.7              | 0                      | 120              | 189k              | 217k              | 11k               | 13k               |

| $vis$ :prodcell $_{15}$ | 24  | 109.3             | 134.3             | 0                      | 253              | 273k              | 330k              | 29k               | 29k               |

| $vis$ :prodcell $_{17}$ | 28  | 211.3             | 253.6             | 0                      | 351              | 322k              | 400k              | $45\mathrm{k}$    | 46k               |

| $vis$ :prodcell $_{18}$ | 14  | 21.4              | 25.5              | 0                      | 78               | 153k              | 171k              | 10k               | 10k               |

| $vis$ :prodcell $_{19}$ | 23  | 61.6              | 71.9              | 0                      | 231              | 260k              | 311k              | 18k               | 18k               |

| $vis$ :prodcell $_{24}$ | 38  | 391.9             | 490.1             | 0                      | 666              | 440k              | 588k              | 60k               | 61k               |

Table 4. Experimental results for dynamic vs. static uniqueness constraints in the induction-step. All times are in seconds. Launches taking less than 10 seconds or having shorter length than 5 has been left out. A superscript "d" means dynamic (on demand) adding of uniqueness constraints. A superscript "s" means static adding of uniqueness constraints between all pairs of states. "Ban" is the number of constraints added (banning two states from being equal). "Clau" is the final number of clauses in the solver. "Conf" is the total number of conflicts in the search-tree of the solver. Only three problems actually needed uniqueness constraints to be provable, and in almost all other cases it incurred a cost to add them. For the three cases where the constraints were necessary, adding them dynamically lead to a speed-up. Without uniqueness constraints these three problem are not provable by induction. The dynamic method thus saves the user from guessing for each problem if uniqueness constraints should be used or not without incurring any extra cost.

#### 5.5 Uniqueness constraints

In the final experiment, we studied the effect of adding uniqueness constraints dynamically and statically, including both instances where the constraints must be added, and instances which are provable without uniqueness constraints. The result is presented in *Table 4*.

The effect of sharpening the constraints by removing variables are not presented, as it is clearly advantageous. A study of the "eijk" equivalence checking problems, where 9 out of 13 need uniqueness constraints, showed that none of these could be solved within the time-bound without using the sharpening.

#### 6 Related Work

Incremental BMC was independently introduced by Ofer Strichman in [Stri01] and Sakallah et. al. in [WKS01]. Our approach differs from previous attempts in that we keep all clauses from previous iterations (including conflict clauses). Moreover, we complete the method with incremental temporal induction. Strichman's work further includes several techniques to enhance the SAT-solving of BMC problems, including internal constraints replication for copying invariant conflict clauses between the time steps of the trace, and BMC specific variable decision strategies [Stri00].

#### 7 Conclusions

Temporal induction has been used before to prove upper bounds for BMC [SSS00]. In these efforts, the authors established it too costly to gradually increase the depth of the induction proof using an external SAT-solver. We have shown that integrating the SAT-solver and the induction procedure overcomes this cost. Furthermore, we sharpened the unique-states constraints by a syntactic analysis on the transition relation; an improvement that was absolutely necessary for many of our benchmarks to go through.

By extensive testing we further reinforced the view that induction is an important complement to BDD-based methods for safety-checking. The combination of techniques presented in this paper results in what the authors believe to be the first efficient and complete induction based checker produced by academia. Enabled by the incremental SAT-interface, we explored an online method of adding uniqueness constraints on demand. To a large extent the method saves the user from deciding manually whether or not to add these constraints, making temporal induction a more push-button technique.

As a side-effect of implementing temporal induction incrementally, we got an incremental BMC for safety properties. The efforts on incremental BMC by [Stri01,WKS01] was based on extensive adaptation of the underlaying SAT-solver. We have shown that results of the same magnitude can be achieved by a much smaller modification of the solver. A standard way of applying BMC

is to generate a single SAT-problem encoding the presence of a bug within k time steps. We have compared this method to iterating up to k incrementally and found that the incremental approach was faster in most cases, even if k was specified as close as 25% above the length of a shortest counter-example.

#### 8 Future Work

The single most significant factor for the success of temporal induction is the induction depth needed. We therefore believe the most important direction of research is towards methods of automatically strengthening the induction-step in order to reduce this depth. A successful method achieving this was presented in [Eijk98,BC00]. It works by finding invariant equivalences or implications between the state variables and internal points. Casting this method into our incremental system looks very promising. Stronger constraints on the shape of a shortest counter-example were suggested in [SSS00], but have not yet been successfully applied. We would like to investigate if a dynamic approach similar to that we used for uniqueness constraints might be helpful.

Finally, there are many possible ways of tuning the SAT-solver to incremental temporal induction. In particular, we wish to explore native uniqueness constraints, as well as the methods presented in [Stri00,Stri01] for specialized variable orderings and constraint replication.

# Acknowledgments

We would like to thank Per Bjesse and Mary Sheeran for their careful reading and valuable criticism of the manuscript for this paper.

#### References

- [BC00] P. Bjesse, K. Claessen. "SAT-based Verification without State Space Traversal" in Formal Methods in Computer-Aided Design, LNCS:1954, Springer-Verlag 2000.

- [BCCZ99] A. Biere, A. Cimatti, E. M. Clarke, and Y. Zhu. "Symbolic model checking without BDDs" in Proc. 8<sup>th</sup> Int. Conf. on Tools and Algorithms for the Construction and Analysis of Systems, LNCS:1579, Springer-Verlag 1999.

- [BCRZ99] A. Biere, E.M. Clarke, R. Raimi, and Y. Zhu. "Verifying safety properties of a PowerPC[tm] microprocessor using symbolic model checking without BDDs" in Proc. 11<sup>th</sup> Int. Conf. on Computer Aided Verification, LNCS:1633, Springer-Verlag 1999.

- [Bry86] R.E. Bryant. "Graph-based algorithms for boolean function manipulation" in *IEEE Trans. on Computers*, C-35(8), Aug. 1986.

- [CAB98] W. Chan, R.J. Anderson, P. Beame, S. Burns, F. Modugno, D. Notkin, J.D. Reese "Model Checking Large Software Specifications" in IEEE Tran. on Software Engineering 24(7), Jul. 1998

- [CFF+01] F. Copty, L. Fix, R. Fraer, E. Giunchiglia, G. Kamhi, A. Tacchella, M.Y. Vardi. "Benefits of bounded model checking at an industrial setting" in Proc. 13<sup>th</sup> Int. Conference on Computer Aided Verification, LNCS:2102, 2001.

- [CS00] K. Claessen, M. Sheeran. "A Tutorial on Lava: A Hardware Description and Verification System" at http://www.cs.chalmers.se/~koen/Lava, 2000

- [DLL62] M. Davis, M. Logman, D. Loveland. "A machine program for theorem proving" in Communications of the ACM, vol 5, 1962.

- [Eijk98] C.A.J. van Eijk. "Sequential equivalence checking without state space traversal" in *Proc. Conf. on Design, Automation and Test in Europe*, 1998.

- [Hok93] J.N. Hooker "Solving the Incremental Satisfiability Problem" in Journal of Logic Programming, vol 15, 1993.

- [MS99] J.P. Marques-Silva, K.A. Sakallah. "GRASP: A Search Algorithm for Propositional Satisfiability" in *IEEE Transactions on Computers*, vol 48, 1999.

- [MZ01] M.W. Moskewicz, C.F. Madigan, Y. Zhao, L. Zhang, S. Malik "Chaff: Engineering an Efficient SAT Solver" in *Proc. of the 38<sup>th</sup> Design* Automation Conference, 2001.

- [Stri00] O. Strichman "Tuning SAT checkers for Bounded Model Checking" in Proc. of 12<sup>th</sup> Intl. Conf. on Computer Aided Verification, LNCS:1855, Springer-Verlag 2000

- [Stri01] O. Strichman "Pruning techniques for the SAT-based Bounded Model Checking Problem" in Proc. 11<sup>th</sup> Advanced Research Working Conf. on Correct Hardware Design and Verification Methods, 2001.

- [SSS00] M. Sheeran, S. Singh, G. Stålmarck. "Checking safety properties using induction and a SAT-solver" in Formal Methods in Computer Aided Design, LNCS:1954, Springer-Verlag 2000.

- [WKS01] J. Whittemore, J. Kim, K. Sakallah. "SATIRE: A New Incremental Satisfiability Engine" in *Proc. 38th Conf. on Design Automation*, ACM Press 2001.

# BMC via On-the-Fly Determinization

Toni Jussila <sup>a,1,2</sup> Keijo Heljanko <sup>b,2,3</sup> Ilkka Niemelä <sup>a,2</sup>

<sup>a</sup> Helsinki University of Technology Laboratory for Theoretical Computer Science P.O. Box 5400, FIN-02015 HUT, Finland

b University of Stuttgart Institute for Formal Methods in Computer Science Universitätsstr. 38, D-70569 Stuttgart, Germany

#### Abstract

The paper develops novel bounded model checking techniques for labelled transition systems. The aim is to increase the efficiency of BMC by exploiting the inherent concurrency in the product of LTSs in order to cover more executions of the product within a given bound. This is done by considering a non-standard execution model, step executions, where multiple actions can take place simultaneously and where component LTSs are determinized on-the-fly, i.e., a component may be in a set of states in a step instead of in just one as in standard interleaving executions. Step executions can be further restricted to a subclass called process executions without loosing reachable states. For bounded model checking of reachability properties of the product of LTSs the paper presents translation schemes from LTSs to a constrained Boolean circuit such that satisfying valuations of the circuit correspond to step (process) executions of the product. The translation schemes have been implemented and some experimental comparisons performed. The results show that the bound needed for step and process executions is in most cases lower than in interleaving executions and that the running time of the model checker using process executions is smaller than using steps. Moreover, the performance compares favorably to a state-of-the-art interleaving BMC implementation in the NuSMV system.

The financial support from Nokia Foundation and Helsinki Graduate School of Computer Science and Engineering is gratefully acknowledged.

$<sup>^2</sup>$  The financial support from the Academy of Finland (Project 53695) is gratefully acknowledged

<sup>&</sup>lt;sup>3</sup> The financial support from the Academy of Finland (grant for research work abroad) is gratefully acknowledged

#### 1 Introduction

Bounded model checking (BMC) is a verification technique that considers only executions of bounded length of the chosen formalism [1]. The general model checking problem for linear temporal logic (LTL) is known to be **PSPACE**-complete, but the bounded case is in **NP** (assuming the used bound to be given in unary encoding). The very idea is to compile the system under verification, the property to be verified and a bound k on the length of the execution to a propositional formula having a model iff the system has an execution of length k that violates the property. The methodology has been successfully applied in industrial setting [2,3].

The aim of the paper is to develop efficient BMC techniques for systems modeled as products of labeled transition systems (LTSs) by exploiting the inherent concurrency in the systems. The basic idea is to cover more executions of a system within a given bound in a way that the size of the encoding is not substantially increased, i.e., it remains linear w.r.t. the bound. The standard approach to BMC is to use interleaving executions where exactly one action is occurring at a time. Here the idea is to encode interleaving executions more compactly by allowing multiple occurrences of actions in different components of the system simultaneously. This kind of an approach has already been investigated using 1-safe Petri nets as the system model and employing step and process executions of Petri nets with encouraging results [10,9].

The novelty in this paper is a technique that exploits independence of actions in the synchronizing product of LTSs so that multiple independent actions can take place in different component LTSs simultaneously. This technique is further combined with an on-the-fly determinization construction where for each component a set of states in which that component can be is maintained. By using determinization the number of different executions the product can have is potentially dramatically reduced, and furthermore invisible transitions do not contribute to the length of an execution. In this work, the concurrent executions of independent actions combined with on-the-fly determinization of components are called *step executions*. Without compromising reachable states, step executions can be further restricted to process executions satisfying an extra condition on visible actions taking place simultaneously.

Based on these ideas a technique for bounded model checking of reachability properties of the synchronizing product of LTSs is developed by devising a translation scheme from the LTSs to a constrained Boolean circuit [12] such that satisfying valuations of the circuit correspond to step executions of the product. A minor extension of the mapping handles process executions. In both cases the size of the encoding is linear w.r.t. the bound. For the encoding, Boolean circuits are employed for clarity and compactness. Such circuits can be translated to propositional formulae in CNF with a linear blow-up by introducing additional propositional variables using standard techniques [12].

The approach has been applied to a set of examples and the data obtained justify the following points. Firstly, the bound needed for step and process executions is in most cases lower than in the traditional interleaving model. Secondly, the running times using process executions are often smaller than using steps. Finally, the results compare favorably to the running times of a state-of-the-art interleaving BMC implementation [6].

The paper is organized as follows. Section 2 introduces the formalism used as the modeling language and Sect. 3 Boolean circuits. Section 4 presents the encoding schemes for both execution models. Section 5 gives test results comparing step and process executions to NuSMV [5,6] and finally Sect. 6 concludes.

## 2 System Modeling Formalism

Concurrent systems specified as labelled transition systems (LTS) are studied in this paper. Three execution models for the synchronized product of n LTSs are introduced. The first is the standard interleaving semantics. Thereafter, the step and process models allowing independent actions to take place simultaneously are defined. The section ends with an analysis on the relation between the different models.

**Definition 2.1** An LTS is a 4-tuple  $L = (S, I, \Gamma, \Delta)$  where

- S is a non-empty set of states,

- $I \subseteq S$  is a non-empty set of *initial* states,

- $\Gamma$  is a non-empty set of visible actions, and

- $\Delta \subseteq S \times (\Gamma \cup \{\tau\}) \times S$ , is the *transition relation*, the elements of which are called transitions of L, where  $\tau$  is the invisible action.

Given n LTSs  $L_1, L_2, \ldots, L_n$ ,  $(L_1 || \ldots || L_n)$  is used to denote their synchronized product defined in the standard way, see e.g. [4] where the states of the product are n-tuples of the states of the components and where a visible action can occur iff all the components containing that action participate. However, in this work the interest is in the finite executions of the product. Firstly, the standard model of interleaving executions are defined.

**Definition 2.2** Let  $L = (L_1 \| \dots \| L_n)$  be the synchronized product of n LTSs. A (finite) interleaving execution  $\sigma_I$  from a state  $s_1$  to a state  $s_{(k+1)}$  of L is a sequence

$$(1) s_1 \xrightarrow{a_1} s_2 \cdots \xrightarrow{a_k} s_{(k+1)}$$

such that each  $s_i = (s_i^1, \ldots, s_i^n), s_i^j \in S_j$ , i.e., each  $s_i^j$  is a state of LTS  $L_j$  and  $a_i \in \Gamma_1 \cup \cdots \cup \Gamma_n \cup \{\tau\}$ . In addition

• for each LTS  $L_j, s_1^j \in I_j$ ,

- for all actions  $a_i$  and LTS  $L_j$ , if  $a_i \in \Gamma_j$  then there is a transition  $(s_i^j, a_i, s_{(i+1)}^j) \in \Delta_j$ , otherwise,  $s_{(i+1)}^j = s_i^j$ , and

- for all actions  $a_i$ , if  $a_i = \tau$  then there is an LTS  $L_j$  such that  $(s_i^j, \tau, s_{(i+1)}^j) \in L_j$  and for any other LTS  $L_l, l \neq j, s_{(i+1)}^l = s_i^l$ .

Let  $pr(\sigma_{\rm I})$  denote the concatenation of the visible actions in  $\sigma_{\rm I}$  in the order mandated by  $\sigma_{\rm I}$ .

A state s' is said to be reachable iff s' is one of the initial states  $I = I_1 \times \ldots \times I_n$  or there is an execution  $\sigma$  from an initial state s to s'. A state s' is a deadlock state iff it is reachable and there is no transition  $(s', a, s'') \in \Delta$ .

**Definition 2.3** Let  $L = (S, I, \Gamma, \Delta)$  and  $S' \subseteq S$ . The  $\tau$ -closure of S' is the set of states  $S'' \subseteq S$  such that  $s \in S''$  iff  $s \in S'$  or there is an execution from some state in S' to s containing only  $\tau$ -transitions.

The following definition presents the step executions of the synchronized product of n LTSs. The model is such that while operating on possibly non-deterministic LTSs it determinizes them on-the-fly. Therefore, in each position in the execution each component may be in a set of states instead of just one.

**Definition 2.4** Let  $L = (L_1 || \cdots || L_n)$  be the synchronized product of n LTSs. A finite step execution  $\sigma_S$  of L is a sequence

$$(2) V_1 \stackrel{A_1}{\to} V_2 \dots V_k \stackrel{A_k}{\to} V_{(k+1)}$$

such that each  $V_i$  is an *n*-tuple  $(S_i^1, \ldots, S_i^n)$ ,  $S_i^j \subseteq S_j$ ,  $1 \le j \le n$ , i.e., each  $S_i^j$  is a set of states of LTS  $L_j$  and each  $\emptyset \subset A_i \subseteq \Gamma_1 \cup \cdots \cup \Gamma_n$ . In addition the following conditions hold:

- In  $V_1$  every  $S_1^j$  is the  $\tau$ -closure of  $I_j$ .

- For each  $A_i$  and  $L_j$ ,  $|A_i \cap \Gamma_j| \leq 1$ , i.e., in each step at most one visible action is executed from each LTS.

- For each  $A_i$ , if  $a \in A_i$ , then for each  $L_j$  such that  $a \in \Gamma_j$  there is a transition  $(s_j, a, s'_j) \in \Delta_j$  such that  $s_j \in S_i^j$ . Furthermore  $S_{(i+1)}^j$  is the  $\tau$ -closure of the set of states reached via all the transitions  $(s', a, s'') \in \Delta_j$  such that  $s' \in S_i^j$ .

- For each  $A_i$  and  $L_j$ , if  $A_i \cap \Gamma_j = \emptyset$  then  $S_{(i+1)}^j = S_i^j$ .

The length of  $\sigma_S$ , denoted by  $|\sigma_S|$ , is k. Let  $lin(\sigma_S)$  denote the set of all possible linearizations of  $\sigma_S$ , i.e., the set of strings  $a_1a_2...a_k$  such that  $a_i \in lin(A_i)$ , for each i = 1, ..., k where  $lin(A_i)$  is the set of strings obtained by concatenating the elements in  $A_i$  in any order.

**Definition 2.5** Let  $L = (L_1 \| \cdots \| L_n)$ ,  $s = (s_1, \dots, s_n)$  and  $V = (S'_1, \dots, S'_n)$ ,  $s_j \in S_j$ ,  $S'_j \subseteq S_j$ ,  $1 \le j \le n$ . Define  $s \subseteq V$  to mean that each  $s_j \in S'_j$ ,  $1 \le j \le n$ .

The following theorems characterize how interleaving and step executions relate to each other. They assume  $L = (L_1 || \dots || L_n)$ .

**Theorem 2.6** Let  $\sigma_I$  be an (interleaving) execution (1) of L and  $|\sigma_I| = k$ . Then there is a step execution  $\sigma_S$

$$(3) V_1 \stackrel{\{a_1\}}{\to} V_2 \dots V_l \stackrel{\{a_l\}}{\to} V_{(l+1)}$$

of L such that  $a_1 a_2 \dots a_l = pr(\sigma_I), l \leq k$  and  $s_{(k+1)} \sqsubseteq V_{(l+1)}$ .

**Theorem 2.7** Let  $\sigma_S$  be a step execution of L reaching  $V_{(k+1)}$ . Then for every state  $s \subset V_{(k+1)}$  there is an interleaving execution  $\sigma_I$  of L reaching s such that  $pr(\sigma_I) \in lin(\sigma_S)$ .

**Corollary 2.8** A state s of  $L = (L_1 || ... || L_n)$  is reachable iff there is a step execution  $V_1 \stackrel{A_1}{\to} V_2 \stackrel{A_2}{\to} ... \stackrel{A_k}{\to} V_{(k+1)}$  such that  $s \sqsubset V_{(k+1)}$  for some k.

The set of step executions for a system contains in most cases different elements intuitively corresponding to the same concurrent behavior. The following addition to Definition 2.4 limits the size without compromising reachable states.

**Definition 2.9** A process execution of L is a step execution of L fulfilling the following condition

• Whenever  $a_i \in A_i, i > 1$  then there is an LTS  $L_j \in L$  such that  $a_i \in \Gamma_j$  and there is an action  $a_k \in A_{i-1} \cap \Gamma_j$ .

A step execution that is not a process execution would be characterized by the fact that in some global state every LTS participating in an action a would be in a state where it could take place. It would not, though, be chosen for immediate execution, but the relevant components would remain in the same states for some steps and only then execute a.

**Theorem 2.10** Let  $\sigma_S$  be step execution of reaching state V. Then there is a process execution  $\sigma_P$  reaching V such that  $|\sigma_P| \leq |\sigma_S|$ .

**Corollary 2.11** A state s of  $L = (L_1 || \dots || L_n)$  is reachable iff there is a process execution  $V_1 \stackrel{A_1}{\to} V_2 \stackrel{A_2}{\to} \dots \stackrel{A_k}{\to} V_{(k+1)}$  such that  $s \sqsubset V_{(k+1)}$  for some k.

Intuitively the process executions are step executions which are in a certain canonical normal form. In fact, this canonical normal form corresponds exactly to the so called Foata normal form [8] from the theory of Mazurkiewicz traces, and also to a partial order semantics for 1-safe Petri nets called processes. For more on this connection, see [9] and further references there.

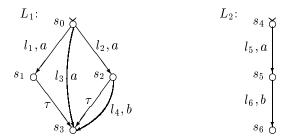

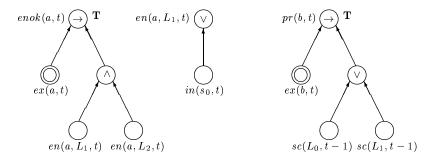

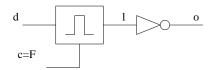

Fig. 1 gives two LTSs, both having the visible actions  $\Gamma_1 = \Gamma_2 = \{a, b\}$ . They will be used as a running example when the elements of the encoding are presented. The encoding assumes, without loss of generality that each visible transition is given a unique label. In the figure, that label is given together with the action associated with the transition.

Fig. 1. Running Example

#### 3 Boolean Circuits

The synchronized products of LTSs are translated to Boolean circuits. This section, based on the presentation of [12], introduces the concept and the associated terminology. A *Boolean circuit* is a directed acyclic graph where the nodes are called *gates*. The gates can be divided to three categories:

- input gates that have no incoming edges nor an associated Boolean function,

- intermediate gates that have both incoming and outgoing edges and an associated Boolean function and

- output gates with incoming edges and an associated Boolean function but no outgoing edges.

A truth valuation for a circuit with gates  $\mathcal{V}$  is a function  $\tau: \mathcal{V} \to \{\text{true}, \text{false}\}$ . A valuation is consistent with the circuit if  $\tau(v) = f(\tau(v_1), \ldots, \tau(v_k))$  for each non-input gate v where f is the Boolean function associated to v and  $v_1, \ldots, v_n$  are the gates with edges to v. The constrained satisfiability problem for Boolean circuits is formulated as follows: given that gates  $c^+ \subseteq \mathcal{V}$  must be true and  $c^- \subseteq \mathcal{V}$  must be false, is there a consistent valuation that respects these constraints, i.e., is there a satisfying valuation? The constrained Boolean circuit satisfiability problem is obviously NP-complete under the plausible assumption that each Boolean function in the system can be evaluated in polynomial time.

The encoding in the present work applies Boolean circuits where the following standard Boolean functions appear as gates:  $\neg$  (negation),  $\lor$  (disjunction),  $\land$  (conjunction), and  $\rightarrow$  (implication). In addition we use a function  $\operatorname{cr}_L^U(v_1,\ldots,v_k)$  which is true in a valuation  $\tau$  iff for the cardinality c of the set  $\{\tau(v)=\operatorname{true}\mid v\in\{v_1,\ldots,v_k\}\}$  holds that  $L\leq c\leq U$  where L and U are fixed constants  $0\leq L\leq U$ . The function  $\operatorname{cr}_L^U$  represents actually a family of functions of which the following two forms are used in the paper:  $\operatorname{cr}_0^1$  (at most one true) and  $\operatorname{cr}_1^1$  (exactly one true).

# 4 Encoding

This section presents the structure of the Boolean circuits encoding the step and process executions of the synchronized product of n LTSs. For representational purposes the gates that appear are given certain illustrative names

briefly explained in Table 1. An in-depth description of them follows in subsequent sections with references to figures of gates drawn from the running example.

Table 1

Translation Predicates

| Gate       | Description                                                      |  |  |  |  |  |

|------------|------------------------------------------------------------------|--|--|--|--|--|

| ex(a,t)    | Action $a$ is executed at time $t$ , input gate.                 |  |  |  |  |  |

| in(s,t)    | Execution is in state $s$ at time $t$ .                          |  |  |  |  |  |

| sc(L,t)    | Component $L$ scheduled at time $t$ .                            |  |  |  |  |  |

| ex(l,t)    | Transition $l$ is executed at time $t$ .                         |  |  |  |  |  |

| uv(L,t)    | Unique visible transition from $L$ at time $t$ .                 |  |  |  |  |  |

| ni(t)      | Disable idling at time $t$ .                                     |  |  |  |  |  |

| enok(a, t) | Execution of action $a$ implies that it is enabled at time $t$ . |  |  |  |  |  |

| en(a,t)    | Action $a$ is enabled at time $t$ .                              |  |  |  |  |  |

The encoding assumes that the LTSs do not have loops containing only  $\tau$ -transitions involving more than one state. If that is the case, the corresponding component can be preprocessed so that the resulting LTS simulates all the executions of the original. The preprocessing step computes the maximal strongly connected components  $C_i$  of the LTS restricted to  $\tau$ -transitions and replaces each  $C_i$  with a single state having as incoming and outgoing transitions the union of those in the set of states in  $C_i$ .

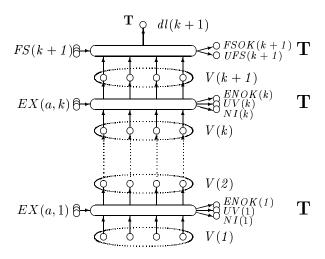

The representation follows certain conventions. The variable k is used to denote the length of the execution and the variables s, t, a and l are used to describe arbitrary states, positions in the execution, actions and transition labels, respectively. Based on the division of gates given in Sect. 3, the circuit is composed as follows. Firstly, some gates, namely those labelled with ex(a,t) act as inputs. This special role is marked with two concentric circles. Secondly, the labels ex(tr,t) and sc(L,t) are attached to intermediate gates. Thirdly, the gates uv(L,t) and ni(t) are outputs constrained to true. This is reflected in the figures in which they appear by the symbol  $\mathbf{T}$  appearing on the right side of the gate.

The gates labelled in(s,t) can appear in different roles based on the value of t. Gates describing the initial states, i.e. in(s,1) are inputs constrained to true and false depending on whether a state s is an initial state or not. For positions  $1 < t \le k$  the gates are intermediate and for the final position, i.e., in(s, k + 1) they are output gates. When the translation scheme is augmented with a circuit detecting reachability properties, these gates are its inputs. The following subsections present the reasoning for all the gates and the section is concluded by a complete translation algorithm.

#### 4.1 Control Flow

For encoding the control flow of the LTSs the idea is that the in(s,t) gates serve to provide information regarding the progress of execution. For any initial state s of an LTS in(s,1) is an input gate and is asserted true. This is in accordance with the fact that in the outset the execution in each component is in the initial states. In general, the execution may be in some state at time t+1 iff one of the following cases is true.

- The state was reached already at t and not left in step t.

- The state is reached due to it belonging to the  $\tau$ -closure of some state reached via actions in step t.

- The state is reached by taking some of its incoming visible transitions in step t.

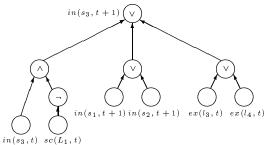

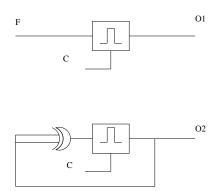

This provides the basis for the definition of the gate in(s, t+1) an instance of which is needed for all the local states for all values  $1 \le t \le k$ . The structure of the gate is given in Fig. 2 for the state  $s_3$  of the running example. It should be noted that  $\tau$ -transitions from a state to itself can (and should) be ignored in the definition.

Fig. 2. Progress of Control Flow

The definition makes use of the sc(L,t) and ex(l,t) gates. The former captures the fact that a component L is scheduled iff a visible action in its alphabet is executed.

The reasoning behind the latter, the ex(l,t) gate, is as follows. A transition is traversed in position t iff the action it is labeled with is executed in position t and the control flow is in its source state. It should be noted that the definition is not circular, but the control flow in position t together with the executed transitions define the control flow in position t + 1. The picture on the right

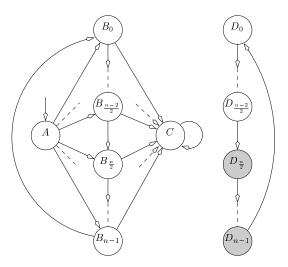

Fig. 3. Elements Illustrating Encoding from Running Example

in Fig. 3 illustrates the gate for the transition  $l_6$  in the running example.

So far, the subcircuits presented have been definitions of the elements used in the encoding. To achieve correspondence with step and later process executions additional constraints need to be imposed. A step (process) execution has the property that only a single visible action is allowed to take place in a single component in each step. The arrangement to handle this is by using a cardinality constraint asserted true. An instance is given in Fig. 3 (the second one from the right).

The encoding may be further enhanced with a gate that disables idling. If such a gate is not added, the resulting circuit encodes step executions up to k whereas with it the executions are of precisely length k. Thus the gate limits the search space. As a downside short deadlocks may be missed if the verification process is started with too large a bound. Idling is disabled iff some visible action is executed, for the running example the gate is the rightmost in Fig. 3.

#### 4.2 Synchronization

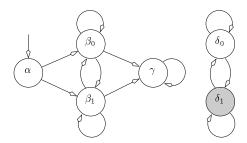

The synchronization of LTSs mandates that a visible action may be executed iff every LTS whose alphabet contains the action participates. So far, this has not been reflected in the subcircuits containing the input gates ex(a,t). The condition is implemented by demanding that the executed action is enabled in each component having that label in its alphabet. An action a is enabled in a component iff it is in some state with an outgoing transition labelled a. The situation for the running example is illustrated in Fig. 4.

Fig. 4. Constraining the Input Gates (left, middle) and Enforcing Scheduling (right)

#### 4.3 Translation Algorithm for Step Executions

Assume  $L = (L_1 || \cdots || L_n)$  and a given bound k. Then the algorithm constructing a Boolean circuit encoding step executions of L of length k is as follows: