Eingereicht von Dipl.-Ing. Daniela Kaufmann, Bsc

Angefertigt am Institut für Formale Modelle und Verifikation

Erstbeurteiler Univ.-Prof. Dr. Armin Biere

Zweitbeurteiler Prof. Jakob Nordström

Mitbetreuung Univ.-Prof. Dr. Manuel Kauers

März 2020

# Formal Verification of Multiplier Circuits using Computer Algebra

Dissertation zur Erlangung des akademischen Grades Doktorin der Technischen Wissenschaften im Doktoratsstudium der Technischen Wissenschaften

> JOHANNES KEPLER UNIVERSITÄT LINZ Altenbergerstraße 69 4040 Linz, Österreich www.jku.at DVR 0093696

# Abstract

Digital circuits are extensively used in computers and digital systems because they are able to represent models for various digital components and arithmetic operations. A subclass of digital circuits are arithmetic circuits, which are used in computer circuits to perform Boolean algebra. It is of high importance to guarantee that these circuits are correct in order to prevent issues like the famous Pentium FDIV bug.

Formal verification can be used to derive the correctness of a given circuit with respect to a certain specification. However, arithmetic circuits, and most prominently gate-level multipliers, impose a challenge for existing verification techniques and in practice still require substantial manual effort. Approaches based on satisfiability checking (SAT) or on decision diagrams seem to be unable to solve this problem in a reasonable amount of time. In principle, theorem provers in combination with SAT are able to verify industrial multipliers, but this approach cannot be applied fully automated. Currently, the most effective automated reasoning technique relies on computer algebra. In this approach the word-level specification, modeled as a polynomial, is reduced by a Gröbner basis, which is implied by the gate-level representation of the circuit. The reduction returns zero if and only if the circuit is correct.

In this thesis we give a rigorous formalization of this reasoning method including soundness and completeness arguments, first for polynomial rings, where the coefficient domain is a field and later for more general polynomial rings. As a consequence we are able to verify not only large unsigned and signed integer multipliers very efficiently, but are also able to verify truncated multipliers. We further improve the algebraic verification approach and present a new incremental column-wise verification algorithm, which splits the verification problem into smaller more manageable sub-problems and thus does not require to consider a full word-level specification. We present preprocessing approaches based on variable elimination in order to rewrite and hence simplify the implied Gröbner basis. However, certain parts of a multiplier, namely final-stage adders, are hard to verify using computer algebra. In our approach we use SAT to replace complex adders by equivalent adders, which can be verified using computer algebra. We develop a dedicated reduction engine, which is able to apply adder substitution and verifies large multipliers of input bit-width 2048 fully automated.

Nonetheless, the verification process might not be error-free. Generating and automatically checking proofs independently increases confidence in the results of automated reasoning tools. We show how the polynomial calculus can be instantiated to yield a practical algebraic calculus (PAC). Proofs in this format can be obtained as a by-product of verifying multiplier circuits in our reduction engine and can be checked with our independent proof checking tools.

# Zusammenfassung

Digitale Schaltungen modellieren digitale Komponenten und arithmetische Operationen und sind daher ein essenzieller Bestandteil in Computern und digitalen Systemen. Arithmetische Schaltungen sind ein Spezialfall von digitalen Schaltungen und werden in Computern genutzt um Boole'sche Algebra zu implementieren. Es ist äußerst wichtig, dass diese Schaltungen korrekt sind, um Fehler wie zum Beispiel den berühmten Pentium-FDIV-Bug zu vermeiden.

Mithilfe von formaler Verifikation kann man feststellen, ob eine gegebene Schaltung ihrer Spezifikation entspricht. Jedoch sind arithmetische Schaltungen, insbesondere Multiplizierer auf Gatterebene, eine Herausforderung für bestehende Verfikationstechniken. Techniken basierend auf dem Entscheidungsproblem der Aussagenlogik (SAT) oder auf Entscheidungsdiagrammen sind nicht der Lage Multiplizerer effizient zu verifizieren. Theorem Prover in Kombination mit SAT können die Korrektheit komplexer Multiplizerer beweisen, allerdings ist diese Methode nicht vollautomatisch anwendbar.

Die zurzeit erfolgreichste Beweistechnik basiert auf Computeralgebra. In dieser Methode wird die Schaltung mithilfe von Polynomen als eine Gröbner Basis modelliert. Die Spezifikation, ebenfalls als Polynom kodiert, wird mittels der Gröbner Basis reduziert. Diese Reduktion liefert das Ergebnis null genau dann, wenn die Schaltung ihrer Spezifikation entspricht.

In dieser Thesis wird dieses Problem einfach, aber präzise formalisiert und Korrektheit und Vollständigkeit wird zuerst für Polynomringe über Körper und nachfolgend für allgemeinere Ringe bewiesen. Dadurch sind wir in der Lage nicht nur vorzeichenlose und -behaftete Integer-Multiplizierer, sondern auch abgeschnittene Multiplizierer zu verifizieren. Wir verbessern diese algebraische Beweistechnik und präsentieren einen neuen inkrementellen Algorithmus, der es erlaubt, das Verifikationsproblem in kleinere Teilprobleme aufzuspalten. Weiters präsentieren wir Vorbearbeitungstechniken, welche Variablen von der Gröbner Basis eliminieren und daher die Polynomdarstellung der Schaltung vereinfachen. Jedoch können gewisse Bestandteile von Multiplizierern, genauer gesagt Addierer, nicht sehr effizient mit Computeralgebra verifiziert werden. Wir nutzen SAT, um diese komplexen Addierer mit einfachen äquivalenten Addierern zu ersetzen. Wir implementieren ein dediziertes Verifikationstool und können Multiplizierer mit Bitbreite 2048 vollautomatisch verifizieren.

Nichtsdestotrotz kann das Verifikationsprogramm Fehler enthalten. Daher werden Beweiszertifikate generiert, welche von eigenständigen Beweischeckern auf Richtigkeit überprüft werden. Wir instanziieren den abstrakten "Polynomial Calculus" und formalisieren das Beweiskalkül PAC. PAC Beweise können in unserem Verifikationstool erzeugt und mit unseren eigenständigen Beweischeckern überprüft werden.

# **Eidesstattliche Erklärung**

Ich erkläre an Eides statt, dass ich die vorliegende Dissertation selbstständig und ohne fremde Hilfe verfasst, andere als die angegebenen Quellen und Hilfsmittel nicht benutzt bzw. die wörtlich oder sinngemäß entnommenen Stellen als solche kenntlich gemacht habe.

Die vorliegende Dissertation ist mit dem elektronisch übermittelten Textdokument identisch.

# Acknowledgements

"Great things are never done by one person. They're done by a team of people."

-Steve Jobs

This thesis would not have been possible without the help and support of many people.

First and foremost, I would like to thank my supervisor Armin Biere for his great and constant support at every phase during my PhD. Armin, thank you for always encouraging me, providing feedback, and most importantly for letting me follow my own research interests.

I am truly grateful to have you as my advisor.

Furthermore, I would like to thank my co-author Manuel Kauers who always has an open ear when it comes to algebra. I really enjoyed our fruitful meetings and discussions. Thank you for supporting me all along the way.

I am thankful to Jakob Nordström for the time and effort to evaluate this work.

I want to thank my colleagues. It was a pleasure to work (and have coffee) with you. A very special gratitude goes to the older PhD generation from our institute, who were great mentors and from whom I learned a lot what it means to be a PhD student.

I would also like to thank my family and friends for their continuous support and patience, not only in the last couple of years but during my whole life.

Last but not least, the biggest thank you goes to the most important person in my life. It's dangerous to go alone – thank you for being part of my life and thank you for your unrestricted courage, wisdom, and power.

# Contents

| Ι | Prologue                                                             | 1     |

|---|----------------------------------------------------------------------|-------|

| 1 | Introduction                                                         | 3     |

|   | 1.1 Outline                                                          | 6     |

|   | 1.2 Contributions                                                    | 6     |

| 2 | Background                                                           | 9     |

|   | 2.1 Multiplier Circuits                                              | 9     |

|   | 2.2 Algebra                                                          |       |

|   | 2.3 Circuit Verification using Computer Algebra                      | 12    |

|   | 2.4 SAT                                                              | 13    |

|   | 2.5 Algebraic Proof Systems                                          | 14    |

|   | 2.6 Related Work                                                     | 15    |

| 3 | Paper A: Incremental Column-Wise Verification of Arithmetic Circ     | cuits |

|   | Using Computer Algebra                                               | 17    |

|   | 3.1 Polynomial Ring                                                  | 18    |

|   | 3.2 Incremental Algorithm                                            | 20    |

|   | 3.3 Reduction Ordering                                               | 21    |

|   | 3.4 Computer Algebra Systems                                         |       |

| 4 | Paper B: A Practical Polynomial Calculus for Arithmetic Circuit Veri | fica- |

|   | tion                                                                 | 27    |

|   | 4.1 Comparison to Polynomial Calculus                                | 28    |

|   | 4.2 Boolean Value Constraints                                        | 28    |

|   | 4.3 Computer Algebra Systems                                         | 32    |

| 5 | Paper C: Verifying Large Multipliers by Combining SAT and Comp       | uter  |

|   | Algebra                                                              | 35    |

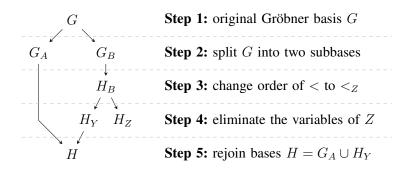

|   | 5.1 Variable Elimination                                             | 36    |

|   | 5.2 Proof Certificates                                               | 38    |

| 6 | Paper D: SAT, Computer Algebra, Multipliers                          | 41    |

|   | 6.1 Proof Generation                                                 | 42    |

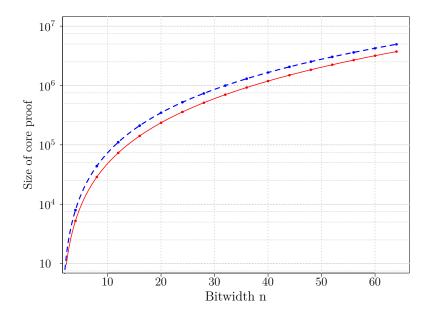

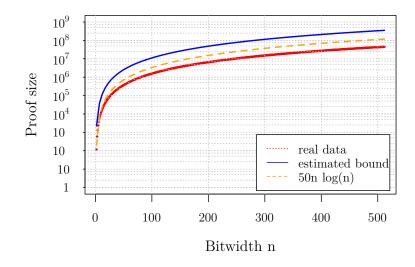

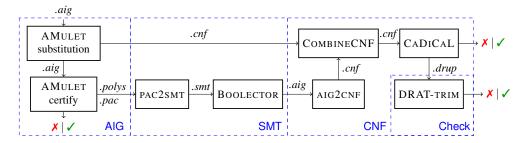

|   | 6.2 Proof Size                                                       | 44    |

| 7 | Paper E: From DRUP to PAC and Back                                   | 45    |

|   | 7.1 DRUP to PAC                                                      | 46    |

|   |                                                                      |       |

#### Contents

|    | 7.2         | PAC to DRUP                                                                     | 48  |

|----|-------------|---------------------------------------------------------------------------------|-----|

| 8  | -           | r F: The Proof Checkers Pacheck and Pastèque for the Practical Alge-            |     |

|    |             | Calculus                                                                        | 51  |

|    | 8.1         | Extensions                                                                      | 52  |

|    | 8.2         | Раснеск                                                                         | 53  |

| 9  | Eval        | uation                                                                          | 57  |

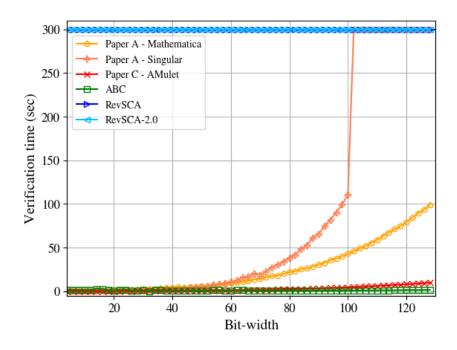

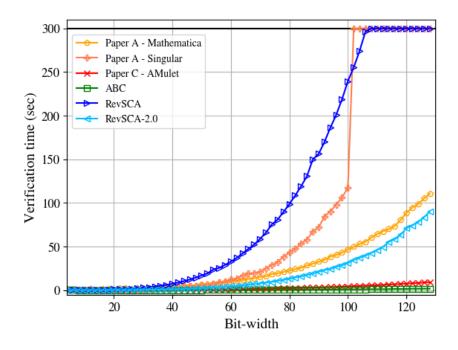

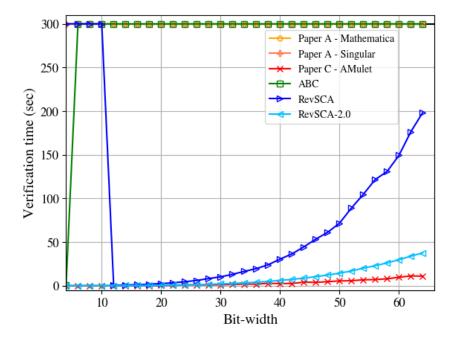

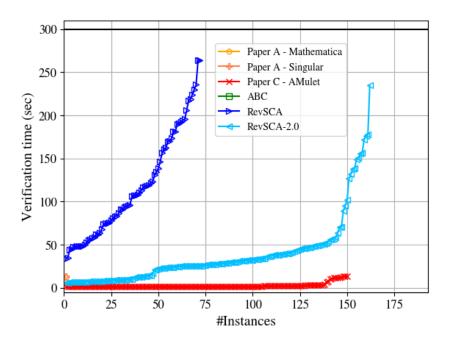

|    | 9.1         | Circuit Verification                                                            | 57  |

|    | 9.2         | Proof Generation and Checking                                                   | 62  |

| 10 | Conc        | clusion                                                                         | 65  |

| II | Par         | Ders                                                                            | 67  |

|    | -           |                                                                                 |     |

| A  |             | emental Column-Wise Verification of Arithmetic Circuits Using Com-<br>r Algebra | 71  |

|    | A.1         | Introduction                                                                    | 72  |

|    | A.2         | Algebra                                                                         | 74  |

|    | A.3         | Ideals associated to Circuits                                                   | 78  |

|    | A.4         | Optimizations                                                                   | 82  |

|    | A.5         | Variable Elimination                                                            | 85  |

|    | A.6         | Order                                                                           | 91  |

|    | A.7         | Incremental Column-Wise Checking                                                | 92  |

|    | A.8         | Incremental Equivalence Checking                                                | 94  |

|    | A.9         | Engineering                                                                     | 97  |

|    |             | Experiments                                                                     |     |

|    |             | Conclusion                                                                      |     |

|    | A.12        | Acknowledgements                                                                | 106 |

| B  | A Pr        | actical Polynomial Calculus for Arithmetic Circuit Verification                 | 109 |

|    | <b>B</b> .1 | Introduction                                                                    |     |

|    | B.2         | Preliminaries                                                                   |     |

|    | B.3         | Practical Algebraic Calculus                                                    |     |

|    | B.4         | Circuit verification using Computer Algebra                                     |     |

|    | B.5         | Engineering                                                                     |     |

|    | B.6         | Experiments                                                                     |     |

|    | B.7         | Conclusion                                                                      | 124 |

| С  |             |                                                                                 | 127 |

|    | C.1         | Introduction                                                                    |     |

|    | C.2         | Specifying Multiplier Circuits                                                  |     |

|    | C.3         | Algebra                                                                         |     |

|    | C.4         | D-Gröbner bases                                                                 | 134 |

#### Contents

|    | C.5    | Variable elimination                                           | 136 |

|----|--------|----------------------------------------------------------------|-----|

|    | C.6    | Combining SAT and Computer Algebra                             | 137 |

|    | C.7    | Experiments                                                    | 141 |

|    | C.8    | Conclusion                                                     | 144 |

| D  | SAT    | , Computer Algebra, Multipliers                                | 147 |

|    | D.1    | Introduction                                                   | 147 |

|    | D.2    | Algebraic approach                                             | 148 |

|    | D.3    | SAT                                                            | 152 |

|    | D.4    | AMulet                                                         | 154 |

|    | D.5    | Proof Generation                                               | 159 |

|    | D.6    | Proof Size                                                     | 161 |

|    | D.7    | Conclusion                                                     | 167 |

| Е  | Fror   | n DRUP to PAC and Back                                         | 169 |

|    | E.1    | Introduction                                                   | 170 |

|    | E.2    | Preliminaries                                                  | 170 |

|    | E.3    | From DRUP to PAC                                               | 173 |

|    | E.4    | From PAC to DRUP                                               | 175 |

|    | E.5    | Experiments                                                    | 178 |

|    | E.6    | Conclusion                                                     | 178 |

| F  | The    | Proof Checkers Pacheck and Pastèque for the Practical Algebrai | c   |

|    | Calc   | culus                                                          | 181 |

|    | F.1    | Introduction                                                   | 181 |

|    | F.2    | Practical Algebraic Calculus                                   | 182 |

|    | F.3    | Pacheck                                                        | 184 |

|    | F.4    | Pastèque                                                       | 185 |

|    | F.5    | Evaluation                                                     | 186 |

|    | F.6    | Conclusion and Future Work                                     | 188 |

|    | F.7    | Appendix                                                       | 189 |

| Bi | bliogr | aphy                                                           | 191 |

# Part I

# Prologue

# Chapter 1 Introduction

"I would hope that computers and computer analysis would lose some of the aura of invincibility with which they have been treated. Computer generated results need to be treated with some enlightened skepticism. No system or microprocessor can be expected to produce results which are absolutely reliable."

-Thomas R. Nicely

Digital circuits carry out logical operations, which makes them an important element in computers and digital systems because they represent models for various digital components and arithmetic operations. The basic function of a digital circuit is to compute binary digital values for the logical function it implements, given binary values at the input. The computation is usually realized by logic gates, which represent simple Boolean functions, such as negation (NOT), conjunction (AND), or disjunction (OR). These logic gates can be combined to build more complex logical operations. A subclass of digital circuits are combinational logic circuits where the output is a function of the present input only, i.e., the output does not depend on previous input values. Combinational logic is used in computer circuits to perform Boolean algebra. For example, the part of an arithmetic logic unit (ALU) in a CPU, which is responsible for mathematical calculations, is constructed using combinational logic. If a circuit implements an arithmetic operation, it is called an *arithmetic circuit*.

Formal verification is used to prove or disprove the correctness of a given software or hardware system with respect to a predefined specification. To this end the system is translated into a mathematical model and automated decision processes are applied to derive the desired correctness properties. The different formal verification approaches are distinguished by the mathematical formalisms used in the verification process.

Formal verification of arithmetic circuits is important to help to prevent issues like the famous Pentium FDIV bug that was detected by Thomas R. Nicely in 1994. This bug affected the floating point unit of early Intel Pentium processors. The division algorithm for floating points used a lookup table to calculate the intermediate quotients. Due to a programming error, five entries of the lookup table contained zero instead of +2. Thus the result was incorrect and in the worst case the error could affect the fourth

#### Chapter 1. Introduction

significant digit of a decimal number. Even more than 25 years after detecting this bug, the problem of formally verifying arithmetic circuits, and especially multiplier circuits, is still considered to be hard.

Up to now several solving techniques have been developed for multiplier verification. A common approach models the problem as a satisfiability (SAT) problem, where the circuit is translated into a formula in conjunctive normal form (CNF). A large set of such encodings was submitted to the SAT Competition 2016 [12]. However, the results indicated that verifying miters of multipliers and other ring properties after encoding them into CNF needs exponential sized resolution proofs [14], which implies exponential run-time of CDCL SAT solvers. This conjecture is neglected in theory in [7], where it was shown that ring properties do admit polynomial sized resolution proofs. However, this theoretical result still needs to be transferred into practice.

Another approach is based on the usage of theorem provers, such as ACL2 [68]. Theorem provers in combination with SAT are able to certify industrial multipliers [54], however, this technique is not fully automated and requires a lot of domain knowledge, since the underlying proof system is based on a problem-specific set of axioms and inference rules. Methods based on term rewriting [97] require domain knowledge too and thus are not fully automated either.

Approaches based on bit-level reverse engineering [86,95] use arithmetic bit-level representations, which are extracted from the given gate-level netlists. This technique is able to verify simple multipliers, but fails to verify non-trivial multiplier architectures.

The first technique that was shown to detect the Pentium bug is based on binary decision diagrams [22], more precisely on binary moment diagrams (BMDs) [29] and variants [30], since their size remains linear in the number of input bits of a multiplier. However, this approach requires structural knowledge of the multipliers [24, 29]. It is important to determine the order in which BMDs are built, because it has tremendous influence on the size and thus performance.

The currently most effective technique for fully automated verification of multipliers is based on computer algebra, e.g., [31,62,80]. In this method all logic gates of the circuit and the specification are represented by polynomials. If the gate polynomials are ordered according to their reverse topological appearance in the circuit, they automatically form a Gröbner basis [25]. As a consequence, the question whether a circuit implements a correct multiplier can be answered by reducing the specification polynomial by the Gröbner basis. The multiplier is correct if and only if the reduction returns zero. The main issue of the algebraic approach is that without preprocessing the size of intermediate reduction results increases drastically.

The aim of this thesis is to investigate and improve formal verification of multiplier circuits using computer algebra to make it practically applicable for non-trivial and optimized multiplier designs. We propose a simple and precise mathematical formalization of the algebraic approach for arithmetic circuit verification, including rigorous proofs of soundness and completeness. We first assume that the coefficient domain is a field in order to use the Gröbner basis theory over fields [25]. In the following, we generalize the approach of circuit verification to be applicable in more general polynomial rings that allow modular reasoning. Modular reasoning allows us to verify not only signed and unsigned integer multipliers, but also truncated multipliers, where the most significant output bits are discarded. These multipliers are used for example in SMT-LIB [5].

Furthermore, we investigate possible reasons of the monomial blow-up in intermediate reduction results. Based on these results we develop reasoning techniques that overcome this issue. One of our technical contributions is a new incremental column-based verification approach for multipliers. In this method the multiplier circuit is divided into several slices and the correctness of the circuit is shown by incrementally verifying the correctness of each slice. The main advantage of this approach is that only one small part of the global specification is used for reduction, which helps to reduce the size of the intermediate results.

We further develop techniques based on variable elimination, which rewrite and simplify the Gröbner basis. In the first version of our rewriting techniques we extract certain subcircuits from the circuit and eliminate the internal variables of these subcircuits from the Gröbner basis. For this optimization we introduce the necessary theory and present a technical theorem that allows us to rewrite only local parts of the Gröbner basis in such a way that the result is again a Gröbner basis. Based on these results we are able to formalize a more general version of variable elimination, which does not require to identify syntactic patterns in the circuits.

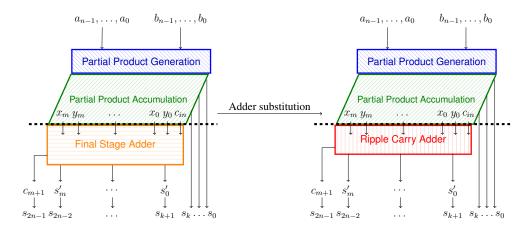

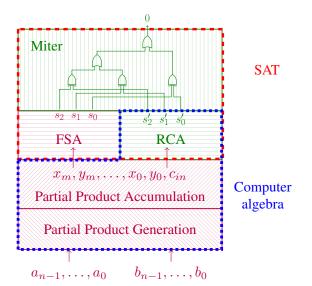

However, certain parts of the multiplier, more precisely particular final stage adders, are hard to verify using computer algebra. These adders usually contain sequences of OR-gates, which lead to an explosion of the intermediate reduction results. On the other hand, equivalence checking of adders is easy for SAT. Based on this observation we combine SAT and computer algebra in our verification technique. We detect whether a multiplier contains a complex final stage adder. If necessary, we replace the complex adder by a simple ripple-carry adder. The correctness of the replacement step is verified by SAT solvers and the rewritten multiplier is verified by computer algebra techniques.

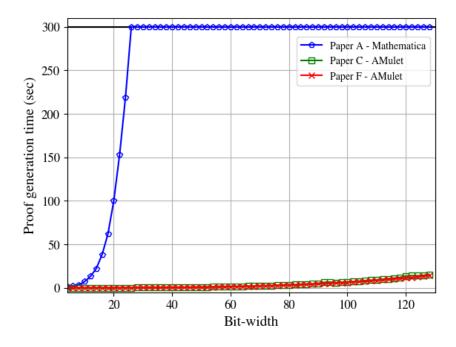

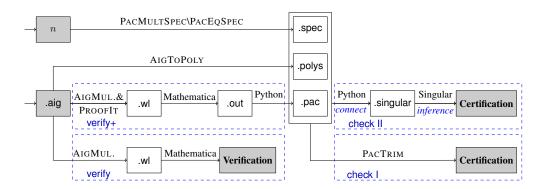

Initially, we use existing computer algebra systems (CAS) to apply Gröbner basis reduction, but these systems are designed for general purposes and thus are slow for our application. Hence, we implement a dedicated reduction engine AMULET, which is tailored to the specific structure of the problem. Implementing our own tool gives a speed-up of three orders of magnitude compared to CAS, cf. Chapter 9.

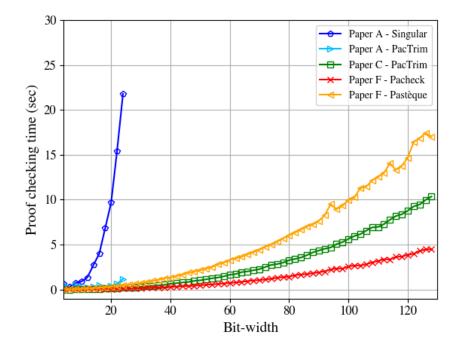

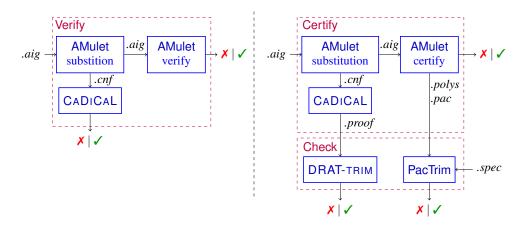

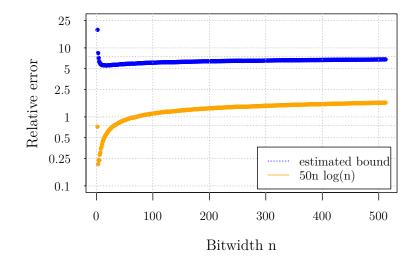

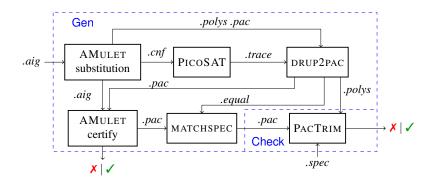

After applying all these sophisticated techniques, we are able to verify the correctness of multipliers. However, the result of automated reasoning tools might not be errorfree. A common approach to increase confidence in the verification results consists of generating proofs, which are checked by independent proof checkers. In order to validate verification techniques based on computer algebra, we show how the abstract polynomial calculus [34] can be instantiated to yield a practical algebraic calculus (PAC), which can be checked efficiently. Proofs in this format can be obtained as by-products in AMULET. We implement independent proof checking tools PACTRIM and PACHECK, where PACHECK is an extension of PACTRIM and supports an extended version of PAC.

Combining SAT and computer algebra has the effect that two proof certificates in different proof formats (DRUP [47] and PAC) are generated. We also investigate how these proof systems can be merged in order to derive one single proof certificate.

### 1.1 Outline

This thesis is structured as a cumulative dissertation and consists of two parts, which allows us to present our work as it was accepted at international conferences and workshops without changing the exposition. The new content of this thesis, contained in Part I, is clearly separated from already published work, which is contained in Part II.

In Part I of the thesis we discuss the contributions of the published Papers A–F, which are included in Part II of this thesis. At first we introduce the background and related work in Chap. 2. In Chap. 3–8 we revisit and reflect on the ideas of Papers A–F. We put our work into context and summarize and analyze the contributions of each paper. We highlight the advantages, but also reflect on downsides, which we noticed in retrospective and lead to new research ideas in later work. In Chap. 9 we give a comprehensive evaluation of our developed techniques that shows the improvement over time. Furthermore, we compare our tools to the current state of the art of related work.

Part II of the thesis, i.e., Paper A–F, consists of six papers [61, 62, 63, 64, 66, 90], where the author of this thesis is the main author <sup>1</sup>. Papers [61, 62, 63, 90] are peerreviewed, [64] is an invited paper published in post-proceedings and [66] is currently under review. The status of the papers is clearly indicated at the beginning of each chapter in Part II. The included papers contain small modifications compared to the original publications such as fixed typos and layout changes to evolve a consistent layout and bibliography. Fixes are clearly stated at the beginning of each chapter. The content of the papers is not modified.

### **1.2 Contributions**

The author of this thesis is the main author of Papers A–F. However, none of the work would have been possible without the help of others. In the following paragraphs we clearly point out the contributions of the author of this thesis.

**Paper A.** [61] *Incremental Column-Wise Verification of Arithmetic Circuits Using Computer Algebra* with Armin Biere and Manuel Kauers. To be published in the Special Issue on Formal Methods in Computer-Aided Design of the International Journal on Formal Methods in System Design (FMSD) and is currently available as "Online First" article. This paper summarizes and extends work presented in [17, 89, 91].

In Paper A, we give a rigorous formalization of the algebraic verification approach. We include a new incremental column-wise verification approach and further improve this algorithm by adding rewriting techniques based on variable elimination.

The formalization was the contribution of all authors and was described by D. Kaufmann. The incremental algorithm was a result of discussions between A. Biere and D. Kaufmann. The rewriting techniques were developed by D. Kaufmann and described with contributions from M. Kauers. The implementation in Mathematica [102] and

<sup>&</sup>lt;sup>1</sup>Please note, some of the work is published under the author's maiden name "Ritirc".

Singular [38] was developed by D. Kaufmann. The first version of the tool AIG-MULTOPOLY, as it is published in [89] was implemented by A. Biere and is since then [17,61,91] extended and maintained by D. Kaufmann. The experimental analysis was performed by D. Kaufmann. The co-authors further contributed with discussions and proofreading Paper A.

**Paper B.** [90] *A Practical Polynomial Calculus for Artihmetic Circuit Verification* with Armin Biere and Manuel Kauers. In Proceedings of the 3rd Workshop on Satisfiability Checking and Symbolic Computation (SC'2) co-located with Federated Logic Conference (FLOC 2018), pages 61–76, Oxford, United Kingdom, 2018.

Paper B presents an algebraic proof calculus (PAC), based on the polynomial calculus, which allows derivation of proof certificates. Proofs in this format can be checked by a CAS or our independent proof checker PACTRIM.

The formalization of the calculus was the result of discussions of all authors and was described by D. Kaufmann. Generating and checking PAC proofs using a CAS was implemented by D. Kaufmann. The first version of PACTRIM, as it is published in Paper B was implemented by A. Biere and is since then extended and maintained by D. Kaufmann. The experimental analysis was performed by D. Kaufmann. The co-authors further contributed with discussions and proofreading Paper B.

**Paper C.** [62] *Verifying Large Multipliers by Combining SAT and Computer Algebra* with Armin Biere and Manuel Kauers. In Proceedings of the 19th International Conference on Formal Methods in Computer Aided Design (FMCAD 2019), pages 28–36, San Jose, CA, USA, 2019.

In Paper C we generalize the algebraic verification approach to be applicable in more general polynomial rings. We combine SAT and computer algebra to substantially improve automated reasoning for circuit verification. Furthermore, we present a rewriting technique that does not involve syntactic pattern matching and implement our dedicated reduction engine AMULET.

The method for combining SAT and computer algebra was developed by D. Kaufmann. The incentive to model circuits in more general polynomial ring was given by D. Kaufmann and was described by all authors. The rewriting technique was established by D. Kaufmann. AMULET was implemented and is maintained by D. Kaufmann. The experimental analysis was performed by D. Kaufmann. The co-authors further contributed with discussions and proofreading Paper C.

**Paper D.** [64] *SAT, Computer Algebra, Multipliers* with Armin Biere and Manuel Kauers. Invited paper in the Post-Proceedings of the 5th and 6th Vampire Workshops, Vampire 2018 and Vampire 2019, pages 1–18, Lisbon, Portugal, 2019.

Paper D extends Paper C and gives a rigorous system description of our tool AMULET. We discuss the algorithms and present how proof certificates are generated in AMULET. Furthermore, we examine the proof size of certain multiplier benchmarks.

#### Chapter 1. Introduction

The system description and the discussion on proof size were performed by D. Kaufmann. The co-authors further contributed with discussions and proofreading Paper D.

**Paper E.** [63] *From DRUP to PAC and Back* with Armin Biere and Manuel Kauers. To be published in Proceedings of the Design, Automation & Test in Europe Conference (DATE 2020), 4 pages, Grenoble, France, 2020.

In the work of Paper C, two proof certificates in different proof formats are generated. For SAT a DRUP proof is generated and for the algebraic approach a PAC proof is generated. In Paper E we investigate how the proof formats can me merged in order to generate only one single proof certificate.

The incentive for translating PAC proofs into DRUP proofs was given by A. Biere. The translation of DRUP proofs into PAC proofs was developed by D. Kaufmann. The techniques in Paper E were described by D. Kaufmann. All developed tools in Paper E were implemented by D. Kaufmann. The experimental analysis was performed by D. Kaufmann. The co-authors further contributed with discussions and proofreading Paper E.

**Paper F.** [66] *The Proof Checkers Pacheck and Pastèque for the Practical Algebraic Calculus* with Mathias Fleury and Armin Biere. Submitted.

In Paper F we present our proof checkers PACHECK and PASTÈQUE. The checker PACHECK checks algebraic proofs more efficiently than PASTÈQUE, which is formally verified using the proof assistant Isabelle/HOL. Furthermore, we extend the practical algebraic calculus of Paper B by adding deletion and extension rules and introduce a more compact syntax.

The incentive for extending the practical algebraic calculus was given by D. Kaufmann. The calculus was described by D. Kaufmann. PACHECK was implemented by D. Kaufmann. PASTÈQUE was implemented and verified in Isabelle/ HOL by M. Fleury. The experimental evaluation was performed by D. Kaufmann. The co-authors further contributed with discussions and proofreading Paper F.

# Chapter 2 Background

This section provides an overview of the background of this thesis. We present the basic structure of multiplier circuits (Sect. 2.1) and give an introduction of computer algebra (Sect. 2.2) and arithmetic circuit verification using computer algebra (Sect. 2.3). Furthermore, we outline SAT (Sect. 2.4) and algebraic proof systems (Sect. 2.5) and conclude this section by discussing related work (Sect. 2.6).

## 2.1 Multiplier Circuits

A digital circuit implements a logical function and computes binary digital values, given binary values at the input. The computation of the function is usually realized by logic gates, such as NOT, AND, and OR. The specification of a circuit is the desired relation between its inputs and outputs. A circuit *fulfills a specification* if for all inputs it produces outputs that match this desired relation. The goal of verification is to formally prove that the circuit fulfills its specification.

In this thesis, we consider gate-level integer multipliers with input bits  $a_0, \ldots, a_{n-1}$ ,  $b_0, \ldots, b_{n-1} \in \{0, 1\}$  and 2n output bits  $s_0, \ldots, s_{2n-1} \in \{0, 1\}$ . If the circuit represents multiplication of unsigned integers, the multiplier is correct if and only if for all possible inputs the following specification holds:

$$\mathcal{L} = -\sum_{i=0}^{2n-1} 2^{i} s_{i} + \left(\sum_{i=0}^{n-1} 2^{i} a_{i}\right) \left(\sum_{i=0}^{n-1} 2^{i} b_{i}\right) = 0$$

(2.1)

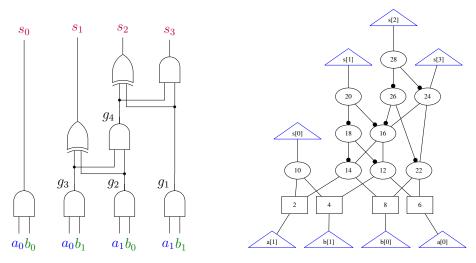

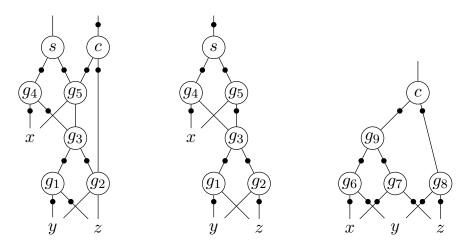

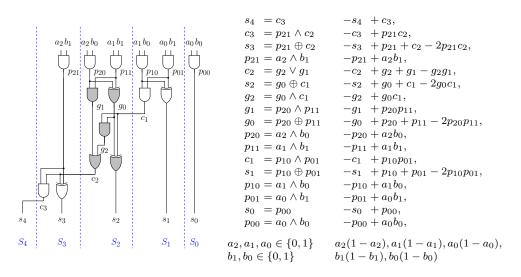

**Example 2.1.** Figure 2.1a shows the gate-level representation of a 2-bit unsigned integer multiplier. The variables  $a_1, a_0, b_1, b_0$  represent the input bits of the multiplier and  $s_3, s_2, s_1, s_0$  are the binary outputs of the multiplier. The word-level specification of this circuit is  $-8s_3 - 4s_2 - 2s_1 - s_0 + (2b_1 + b_0)(2a_1 + a_0) = 0$ .

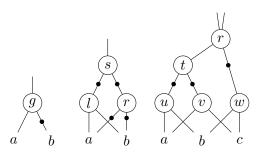

A common representation of combinational circuits is the encoding as an And-Inverter-Graph (AIG) [70]. An AIG is a special case of a directed acyclic graph, and consists only of two-input nodes representing logical conjunction. The edges of an AIG may contain a marking that indicates logical negation. The AIG representation of a circuit is usually larger, i.e., contains more nodes, than the gate-level representation, but is very efficient to manipulate. In this thesis all circuits are given as AIGs. Figure 2.1b shows the AIG representation of the multiplier depicted in Fig. 2.1a.

(a) Gate-level representation of 2-bit multiplier. (b)

(b) AIG representation of 2-bit multiplier.

Figure 2.1: Graph representation of 2-bit multipliers.

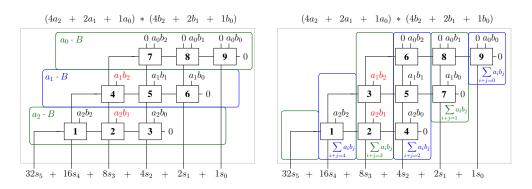

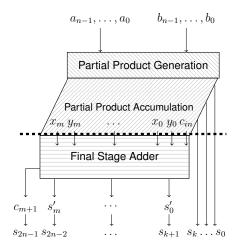

The space and time complexity of a multiplier circuit depends highly on its architecture. Multiplier circuits can generally be decomposed into three components [85]. In the first component, *partial product generation* (PPG), the partial products  $a_ib_j$  for  $0 \le i < n$ ,  $0 \le j < n$ , as contained in the specification, are generated. This can for example be achieved by using simple AND-gates or using a more complex Booth encoding [85].

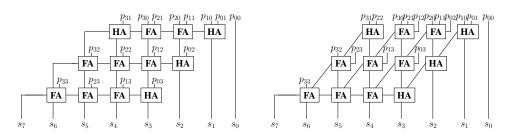

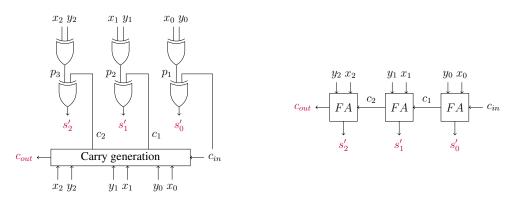

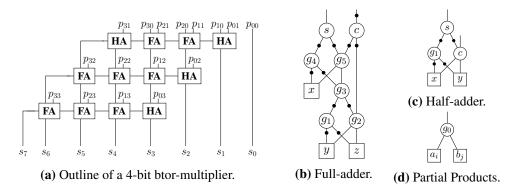

In the second component, *partial product accumulation* (PPA), multi-operand addition is performed using full- and half-adders to reduce the partial products to two layers. Well-known accumulation structures are array accumulation, diagonal accumulation, Wallace trees, or compressor trees [85].

In the *final-stage adder* (FSA) the output of the circuit is computed using an adder circuit. Generally, adder circuits can be split into two groups: either the carries are computed alongside the sum bits or they are calculated before the sums. Adders of the first group consist of a sequence of half- and full-adders, giving them a simple but inefficient structure. Examples are ripple-carry adders or carry-select adders. In order to decrease the latency of carry computation, the adder circuits of the second group precompute the carry bits of the adder. They are called *generate-and-propagate (GP) adders*. Examples are carry look-ahead adders and Kogge-Stone adders [85].

We call multipliers, that can be fully decomposed into full- and half-adders *simple multipliers*, all other architectures are called *complex multipliers*.

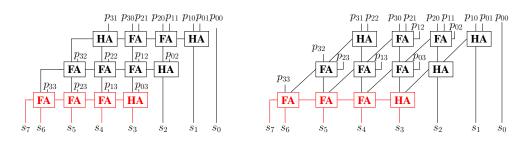

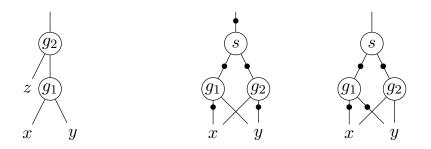

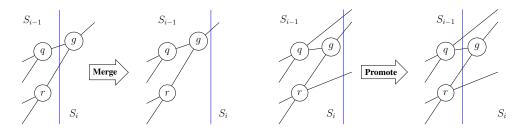

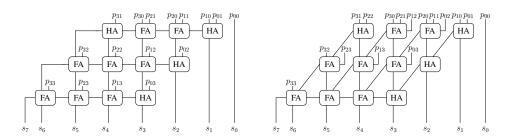

**Example 2.2.** Figure 2.2 shows two simple multiplier architectures with input bitwidth 4. In both circuits the PPG uses AND-gates, i.e.,  $p_{ij} = a_i \wedge b_j$ . In "btor"-multipliers [83], which are shown on the left side, the partial products are accumulated using an array structure. The "sp-ar-rc"-multipliers [53] (also called "sparrc" in this thesis), which are depicted on the right side, use a diagonal structure. In both multipliers, the FSA is a ripple-carry adder, which is highlighted in red.

Figure 2.2: Architecture of "btor" (left) and "sp-ar-rc" (right) multipliers.

## 2.2 Algebra

In this section we introduce algebraic concepts, following [35]. Throughout this section let  $\mathbb{K}[X] = \mathbb{K}[x_1, \ldots, x_n]$  denote the ring of polynomials in variables  $x_1, \ldots, x_n$  with coefficients in a field  $\mathbb{K}$ .

- A term τ is a product of the form τ = x<sub>1</sub><sup>e<sub>1</sub></sup> ··· x<sub>n</sub><sup>e<sub>n</sub></sup> for certain e<sub>1</sub>,..., e<sub>n</sub> ∈ N. A monomial m = ατ is a constant multiple of a term, with α ∈ K. A polynomial p = m<sub>1</sub> + ··· + m<sub>s</sub> is a finite sum of monomials.

- On the set of terms an order  $\leq$  is fixed such that for all terms  $\tau, \sigma_1, \sigma_2$  we have  $1 \leq \tau$  and  $\sigma_1 \leq \sigma_2 \Rightarrow \tau \sigma_1 \leq \tau \sigma_2$ .

- A term order is called a *lexicographic term order* if for all terms σ<sub>1</sub> = x<sub>1</sub><sup>u<sub>1</sub></sup> ··· x<sub>n</sub><sup>u<sub>n</sub></sup>, σ<sub>2</sub> = x<sub>1</sub><sup>v<sub>1</sub></sub> ··· x<sub>n</sub><sup>v<sub>n</sub></sup> we have σ<sub>1</sub> < σ<sub>2</sub> iff there exists an index *i* with u<sub>j</sub> = v<sub>j</sub> for all *j* < *i*, and u<sub>i</sub> < v<sub>i</sub>.

</sup>

- Every polynomial p ≠ 0 contains only finitely many terms, the largest of which (w.r.t. the chosen order ≤) is called the *leading term* and denoted by lt(p).

- If  $p = \alpha \tau + \cdots$  and  $\operatorname{lt}(p) = \tau$ , then  $\operatorname{lc}(p) = \alpha$  is called the *leading coefficient* and  $\operatorname{lm}(p) = \alpha \tau$  is called the *leading monomial* of p. We call  $p - \alpha \tau$  the *tail* of p.

- For a given set of polynomials P = {p<sub>1</sub>,..., p<sub>m</sub>} ⊆ K[X], a model is a point u = (u<sub>1</sub>,..., u<sub>n</sub>) ∈ K<sup>n</sup> such that for all p<sub>i</sub> ∈ P we conclude that p<sub>i</sub>(u<sub>1</sub>,..., u<sub>n</sub>) = 0.

- A nonempty subset  $I \subseteq \mathbb{K}[X]$  is called an *ideal* if  $\forall p, q \in I : p + q \in I$  and  $\forall p \in \mathbb{K}[X] \forall q \in I : pq \in I$ .

- If I ⊆ K[X] is an ideal, then a set P = {p<sub>1</sub>,..., p<sub>m</sub>} ⊆ K[X] is called a *basis* of I if I = {q<sub>1</sub>p<sub>1</sub> + ··· + q<sub>m</sub>p<sub>m</sub> | q<sub>1</sub>,..., q<sub>m</sub> ∈ K[X]}. We say I is generated by P and write I = ⟨P⟩.

- A basis P = {p<sub>1</sub>,..., p<sub>m</sub>} of an ideal I ⊆ K[X] is called a Gröbner basis (w.r.t. the fixed order ≤) iff ∀q ∈ I∃p<sub>i</sub> ∈ P : lm(p<sub>i</sub>) | lm(q).

- Every ideal of  $\mathbb{K}[X]$  has a Gröbner basis, and there is an algorithm which, given an arbitrary basis of an ideal, computes a Gröbner basis of it [25].

#### Chapter 2. Background

The theory of Gröbner bases offers a decision procedure for the so-called ideal membership problem, i.e., given  $q \in \mathbb{K}[X]$  and a basis  $P = \{p_1, \ldots, p_m\} \subseteq \mathbb{K}[X]$ , decide whether q belongs to the ideal generated by  $p_1, \ldots, p_m$ . If  $\{p_1, \ldots, p_m\}$  is a Gröbner basis, then the question can be answered using a multivariate version of polynomial division with remainder. The polynomial q belongs to  $\langle P \rangle$  if and only if the remainder of division of q by P is zero. More facts of Gröbner bases are:

- Let q ∈ K[X] and P = {p<sub>1</sub>,..., p<sub>m</sub>} ⊆ K[X]. The remainder r of the division of q by P is a polynomial such that q − r is contained in the ideal generated by P and r is reduced w.r.t. P, which means it does not contain any term that is a multiple of one of the leading terms lt(p<sub>1</sub>),..., lt(p<sub>m</sub>).

- Let  $P \subseteq \mathbb{K}[X] \setminus \{0\}$ , and define

$$\operatorname{spol}(p,q) := \operatorname{lcm}(\operatorname{lt}(p),\operatorname{lt}(q))\left(\frac{p}{\operatorname{lm}(p)} - \frac{q}{\operatorname{lm}(q)}\right)$$

for all  $p, q \in \mathbb{K}[X] \setminus \{0\}$ , with lcm the least common multiple. Then P is a Gröbner basis if and only if the remainder of the division of  $\operatorname{spol}(p,q)$  by P is zero for all pairs  $(p,q) \in P \times P$ .

If p, q ∈ K[X] \ {0} are such that their leading terms lt(p), lt(q) have no variables in common, then the division of spol(p, q) with {p, q} has remainder zero. This property is known as *Buchberger's product criterion*.

In this section we restricted  $\mathbb{K}$  to be a field. We present the algebraic background for coefficient domains R, where R is a commutative ring with unity, in Paper C, where we generalize the theory to be applicable in more general polynomial rings.

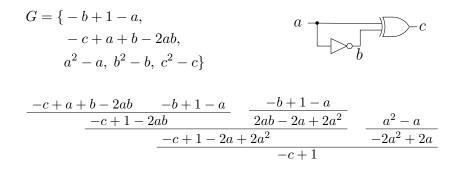

#### 2.3 Circuit Verification using Computer Algebra

In this section we give a short introduction of circuit verification using computer algebra, a rigorous formalization of this approach can be found in Paper A. We consider circuits with 2n inputs  $a_0, \ldots, a_{n-1}$  and  $b_0, \ldots, b_{n-1}, 2n$  outputs  $s_0, \ldots, s_{2n-1}$ , and a number of logical gates, denoted by  $g_1, \ldots, g_k$ . By R we denote the ring  $\mathbb{K}[a_0, \ldots, a_{n-1}, b_0, \ldots, b_{n-1}, g_1, \ldots, g_k, s_0, \ldots, s_{2n-1}] = \mathbb{K}[X]$ .

The semantic of each circuit gate implies a polynomial relation among the input and output variables, such as the following ones:

| $u = \neg v$     | implies | 0 = -u + 1 - v        |       |

|------------------|---------|-----------------------|-------|

| $u = v \wedge w$ | implies | 0 = -u + vw           | (2,2) |

| $u=v\vee w$      | implies | 0 = -u + v + w - vw   | (2.2) |

| $u=v\oplus w$    | implies | 0 = -u + v + w - 2vw. |       |

We call these polynomials *gate polynomials* or *gate constraints*. Let  $G \subseteq R$  be the set of polynomials, which contains for each gate of the given circuit the corresponding polynomial of Eqn. (2.2).

To enforce that our variables are Boolean and can have only the values 0 and 1, we add for each variable  $x \in X$  the relation x(x - 1) = 0. In Papers A and B we call these polynomials *field polynomials*. We renamed the definition in Paper C to *Boolean value constraints*, because the term "field" may suggest a connection to the coefficient field K.

We order the set of terms according to a lexicographic term order, where the output variable of a gate is always greater than the input variables of a gate. Such an ordering is called *reverse topological term order* [78]. Because of Buchberger's product criterion and the structure of the gate polynomials, the gate polynomials together with the Boolean value constraints define a Gröbner basis for the ideal generated by the gate polynomials and Boolean value constraints. Thus the correctness of the circuit can be shown by reducing the specification  $\mathcal{L}$  by the gate polynomials using polynomial reduction and checking whether the result is zero.

### 2.4 SAT

We briefly introduce the SAT problem, following [47].

- A *literal* l is either a positive Boolean variable x or its negation  $\overline{x}$ .

- A *clause* C is a finite disjunction of literals. If a clause contains only one literal, we call it a *unit clause*.

- A formula in conjunctive normal form (CNF) F is a finite conjunction of clauses.

- An assignment  $\tau$  is a function that consistently maps the literals of F to  $v \in \{\mathbf{t}, \mathbf{f}\}$ , such that  $\tau(x) = v \Leftrightarrow \tau(\overline{x}) = \neg v$ , where  $\neg \mathbf{t} = \mathbf{f}$  and  $\neg \mathbf{f} = \mathbf{t}$ .

A formula evaluates to **t** if and only if every clause in the formula evaluates to **t**. A clause C evaluates to **t** if there exists a literal  $l \in C$  with  $\tau(l) = \mathbf{t}$ . Given a CNF formula F, the SAT problem is to decide if there exists an assignment such that F evaluates to **t**. If such an assignment exists, the formula is *satisfiable*, otherwise it is *unsatisfiable*.

A clause C is *redundant* w.r.t. a formula F, if  $F \wedge C$  is satisfiable iff F is satisfiable. Redundant clauses are for example derived using *resolution* [92]: Given two clauses  $C_1 = (a \lor x_0 \lor \ldots \lor x_m)$  and  $C_2 = (\overline{a} \lor y_0 \lor \ldots \lor y_n)$  the clause  $C = (x_0 \lor \ldots \lor x_m) \lor x_m \lor y_0 \lor \ldots \lor y_n$  can be resolved.

A common technique used in SAT solvers is called *unit propagation*: If a formula F contains a unit clause C = l, remove all clauses containing l and all occurrences of  $\overline{l}$ .

If a formula is satisfiable a satisfying assignment is a witness. However, if the formula is unsatisfiable more involved reasoning is required to derive proofs of unsatisfiability, also called *refutation*. This is done by showing that the empty clause is redundant. Providing certificates of unsatisfiability is mandatory in the SAT Competitions since 2013.

Standard refutation proof formats are either resolution proofs or clausal proofs. Clausal proofs are easier to generate and are more compact than resolution proofs. The most basic clausal proof format is *reverse unit propagation* (RUP) [41]. Let  $\overline{C}$

#### Chapter 2. Background

denote the negation of a clause C. If for example  $C = a \lor b \lor \overline{x}$  then  $\overline{C} = \overline{a} \land \overline{b} \land x$ . We say C is a *RUP clause* if  $F \land \overline{C}$  evaluates to **f** only by *unit propagation*. A RUP proof is a sequence of RUP clauses containing the empty clause.

A *delete reverse unit propagation* (DRUP) [49] proof extends RUP by adding deletion information to decrease the cost of proof validation [99]. Clausal DRUP proofs are checked through unit propagation. As a side effect a resolution proof can be produced.

### 2.5 Algebraic Proof Systems

Algebraic proof systems reason over polynomials in  $\mathbb{K}[X]$ , where  $\mathbb{K}$  is a field and the variables  $X = \{x_1, \ldots, x_l\}$  represent Boolean values. Thus it holds for each  $x_i \in X$ , that  $x_i^2 - x_i = 0$ . The aim of an algebraic proof is to derive a refutation, i.e., derive that a given set of polynomials  $P = \{p_1, \ldots, p_m\} \subseteq \mathbb{K}[X]$  together with the Boolean value constraints  $B(X) = \{x_i^2 - x_i \mid x_i \in X\}$  has no common roots. In algebraic terms this means to show that the constant polynomial  $1 \in \langle P \cup B(X) \rangle$ .

In the following we present two very common proof formats, which are able to derive a refutation using algebraic reasoning methods.

#### 2.5.1 Polynomial Calculus

The first proof system is the *polynomial calculus* (PC) [34]. A proof in PC is a sequence of proof rules  $R = (r_1, \ldots, r_n)$ , which model the properties of an ideal. A PC proof is a correct refutation when the constant polynomial 1 is derived. Each rule has the following form:

| Axiom              | $p_i$                             | $p_i \in P$                                                      |

|--------------------|-----------------------------------|------------------------------------------------------------------|

| Boolean Axiom      | $\overline{x_j^2 - x_j}$          | $x_j \in X$                                                      |

| Linear combination | $\frac{p  q}{\alpha p + \beta q}$ | $p,q$ appearing earlier in the proof $\alpha,\beta\in\mathbb{K}$ |

| Multiplication     | $rac{p}{	au p}$                  | $p$ appearing earlier in the proof $\tau$ any term               |

The polynomial calculus with resolution (PCR) [3] extends PC by adding a negation rule, which models that a new variable  $\overline{x_i}$  is the logical negation of  $x_i$ .

Negation

$$\overline{x_j + \overline{x_j} - 1}$$

Since  $\overline{x_i}$  is a newly added variable, PCR operates in the ring  $\mathbb{K}[x_1, \ldots, x_l, \overline{x_i}, \ldots, \overline{x_l}]$ .

Adding new variables makes it possible to produce shorter proofs, as we will discuss later in Sect. 7.1.2.

#### 2.5.2 Nullstellensatz

The second algebraic proof system we consider is Nullstellensatz [6]. A Nullstellensatz refutation of a set of polynomials  $P = \{p_1, \dots, p_m\} \subseteq \mathbb{K}[X]$  is an equality

$$\sum_{i=1}^{m} q_i p_i + \sum_{j=1}^{l} r_j (x_j^2 - x_j) = 1,$$

(2.3)

with  $q_i, r_j \in \mathbb{K}[X]$ .

## 2.6 Related Work

In recent years great progress has been achieved on verifying (integer) multiplier circuits using computer algebra. We consider the work of Sayed-Ahmed et al. [93,94], Mahzoon et al. [79, 80] and, Yu et al. [31, 32, 103, 104, 106] the most related work, as their research also focuses on verification of integer multipliers using computer algebra. The work of Lv et al. [77, 78] focuses on Galois field multipliers. In contrast to word-level verification the work of Brickenstein et al. [20] proposes bit-level equivalence checking of multipliers.

**Sayed-Ahmed et al.** [93,94] The authors of [93] designed a dedicated polynomial reduction engine and also present various syntactic rewriting optimizations, which makes their algebraic technique scale to large non-trivial multiplier designs of various architectures. In follow-up work [94] they propose an algebraic variant of combinational equivalence checking, also based on Gröbner basis theory. It is similar to SAT sweeping [70], and compares circuits bit-wise, i.e., output by output. However, their tools of [93,94] are not available, nor are details about the experiments.

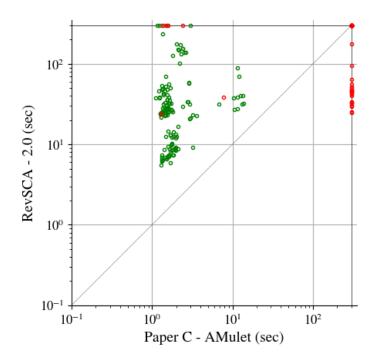

**Mahzoon et al.** [79,80] Vanishing monomials are monomials that occur in intermediate results and evaluate to zero during the reduction process. In [79] Mahzoon et al. discuss why vanishing monomials occur and propose a method, which searches for converging gate cones and allows local cancellation of the vanishing monomials before global backward rewriting is applied in order to prevent an explosion of the intermediate reduction results. In [80] the authors present a further optimization, which is able to detect so-called "atomic blocks" in order to speed-up rewriting by reducing the search space for finding converging gates. This approach is very successful in verifying a large variety of multiplier architectures but is an order of magnitude slower than our approach of Paper C, as we will show in Chap. 9.

**Yu et al.** [31, 32, 103, 104, 106] In [32, 103] the authors use *function extraction*, a similar algebraic approach to Gröbner basis reduction. The word-level output of the circuit is rewritten using the gate relations and the goal is to derive a unique polynomial representation of the circuit inputs. In order to verify correctness of the circuit, this polynomial is then compared to the circuit specification. In follow-up work [31, 106]

#### Chapter 2. Background

full- and half-adders are identified and replaced by polynomials to simplify the set of polynomials. Their technique is able to handle very large clean multipliers efficiently but fails on slightly optimized multiplier architectures. The authors also extended their work to Galois field multipliers [104].

**Brickenstein et al.** [20] The authors of [20] design a framework for Gröbner basis computations with Boolean polynomials. They introduce a specialized data structure based on zero-suppressed binary decision diagrams, which allows efficient manipulation of Boolean polynomials. Their approach is able to apply bit-wise equivalence checking of integer multiplier circuits, but handles only small-size multipliers.

Lv et al. [77,78] The authors of [77,78] use an algebraic approach to verify Galois field multipliers. The multiplier circuit is modeled as a polynomial system in  $\mathbb{F}_{2^k}[X]$  and consequently Gröbner basis theory over Galois fields is used to derive the correctness of the multiplier.

## Chapter 3

# Paper A: Incremental Column-Wise Verification of Arithmetic Circuits Using Computer Algebra

In Paper A we first give a comprehensive formalization of arithmetic circuit verification using computer algebra and prove soundness and completeness. The general idea of arithmetic circuit verification using computer algebra is to model each gate by corresponding polynomial equations, called *gate constraints*. Correctness of the circuit is derived by showing that the specification  $\mathcal{L}$ , like Eqn. (2.1), represented as a polynomial, is contained in the ideal generated by the gate constraints. In this section we consider circuits with 2n inputs  $a_0, \ldots, a_{n-1}, b_0, \ldots, b_{n-1}$  and 2n outputs  $s_0, \ldots, s_{2n-1}$ .

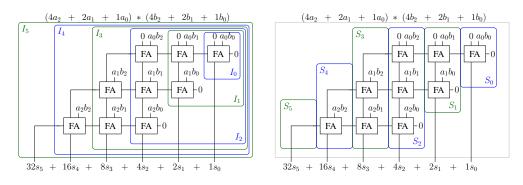

In order to optimize the practical application of arithmetic circuit verification using computer algebra, we present a novel incremental column-wise verification algorithm, which allows us to split the verification problem into smaller, more manageable subproblems. The multiplier is partitioned into slices, such that each slice contains exactly one output bit. For each slice we derive corresponding slice-wise specifications, which in contrast to the word-level specification, only contain a linear number of partial products. Correctness of the multiplier is derived by verifying each slice incrementally.

To further enhance the practical approach we present a preprocessing technique, which rewrites the Gröbner basis implied by the gate constraints. We search and identify certain structures, namely full- and half-adders, XOR-gates and gates with only one parent, in the input AIG. Internal variables of these patterns are eliminated from the Gröbner basis. We prove a technical theorem that allows us to rewrite only local parts of the Gröbner basis without violating the Gröbner basis property. By eliminating internal nodes of full- and half-adders and XOR-gates, we only represent the specification of these structures in the Gröbner basis instead of the direct translation of all internal nodes. For full- and half-adders these polynomials are linear and thus significantly reduce the blow-up of the intermediate reduction results.

We implement a tool, called AIGMULTOPOLY, which translates multipliers given as AIGs into a set of polynomials and applies the described preprocessing steps. The output file is passed to the CAS Mathematica [102] or Singular [38] that apply the polynomial reduction. Our experiments show that by using these techniques we are able to verify simple multipliers but fail to verify complex multipliers.

#### Chapter 3. Paper A - Discussion

We furthermore present how the incremental verification algorithm can be generalized to allow equivalence checking of circuits. In equivalence checking a circuit is compared to a so-called golden model, which is a circuit that is known to be correct. The benefit of equivalence checking, in comparison to circuit verification is that the specification of the circuit does not need to be known. In our approach we apply equivalence checking as follows. Let  $S = \sum_{i=0}^{n} 2^i s_i$  be the output bit-vector of the circuit whose correctness is in question and let  $S' = \sum_{i=0}^{n} 2^i s'_i$  be the output of the golden model. The gates of both circuits are encoded as polynomials and we check whether the polynomial S - S' = 0 is contained in the ideal generated by the circuit constraints and the Boolean value constraints. However, this has the effect that actually both circuits are verified simultaneously. It can be seen in the experiments of Paper A that equivalence checking of multipliers needs twice as much time than verifying one single multiplier. Since we are able to define a specification for multipliers, we favor direct verification of multiplier circuits over equivalence checking with the golden model and we do not apply equivalence checking of circuits in follow-up work of circuit verification.

### 3.1 Polynomial Ring

Initially we wanted to work in the ring  $\mathbb{Z}[X]$ , because  $\mathbb{Z}$  is the ring whose multiplication we want to describe. However,  $\mathbb{Z}$  is not a field and we cannot use the basic Gröbner bases theory over fields [25]. Since  $\mathbb{Q}$  is a field, which contains  $\mathbb{Z}$ , we fixed the polynomial ring to  $\mathbb{Q}[X]$  in Paper A. Additionally, the reduction algorithms in Mathematica and Singular are much slower for  $\mathbb{Z}[X]$  than for  $\mathbb{Q}[X]$ . Furthermore, we noticed that because the leading coefficients of the polynomials are all -1, our whole computation stays in the ring  $\mathbb{Z}[X]$  anyhow.

In retrospective, modeling the verification problem in  $\mathbb{Q}[X]$  is not optimal and limits the power of our procedure. The reason is that certain multiplier architectures invoke chains of XOR-gates to compute the most significant output bit  $s_{2n-1}$ . For example, this always happens in our benchmarks, when Booth encoding is used to generate the partial products. The corresponding coefficient of  $s_{2n-1}$  in the word-level specification is  $2^{2n-1}$ . Hence, reduction by a polynomial, which encodes an XOR-gate generates a monomial  $-2^{2n}vw$ , cf. Eqn. (2.2), where either v or w represents again the output variable of an XOR-gate. Thus reducing  $s_{2n-1}$  by the polynomials encoding the XORgates yields multiple monomials with coefficients that are multiples of  $2^{2n}$ , which will reduce to zero later in the verification procedure. However, these non-linear monomials have to be rewritten first and thus increase the results of the intermediate reduction results until they are canceled.

We discuss in Paper C that it is a better choice to select the ring  $\mathbb{Z}_{2^l}[X]$ , where l is the number of output bits. This has the effect that any monomial, which is a multiple of  $2^l$ , is directly eliminated. We prove that we maintain soundness and completeness by choosing l as the number of output bits. Selecting  $\mathbb{Z}_{2^l}[X]$  does not only make verification of unsigned and signed integer multipliers much more efficient, but also allows verification of truncated multipliers, were the n most significant bits are discarded.

| polynomial ring          | sec  | max     | $S_7$ | $S_6$ | $S_5$ | $S_4$ | $S_3$ | $S_2$ | $S_1$ | $S_0$ |

|--------------------------|------|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| $\mathbb{Q}[X]$          | 0.07 | 2 2 6 4 | 2     | 25    | 57    | 94    | 358   | 157   | 36    | 36    |

| $\mathbb{Z}_{2^{2n}}[X]$ | 0.00 | 36      | 2     | 7     | 12    | 14    | 15    | 14    | 6     | 5     |

Table 3.1: Number of monomials in intermediate results for 4-bit "bp-ar-rc" multiplier.

We show in Paper C that the ideal membership problem in  $\mathbb{Z}_{2^l}[X]$  for an ideal I can be converted into an ideal membership problem in the ring  $\mathbb{Z}[X]$ . Whenever we want to decide whether a polynomial  $q \in I \subseteq \mathbb{Z}_{2^l}[X]$  we can instead check whether  $q \in I + \langle 2^l \rangle \subseteq \mathbb{Z}[X]$ . For the latter we can use the theory of D-Gröbner bases [9, 76].

**Example 3.1.** Consider a 4-bit "bp-ar-rc"-multiplier [53]. This multiplier is very similar to the "sp-ar-rc"-multiplier shown in Fig. 2.2, except that the partial-products are generated using a Booth encoding instead of simple AND-gates. We apply our incremental column-wise verification algorithm in  $\mathbb{Q}[X]$  and  $\mathbb{Z}_{2^{2n}}[X]$  using our tool AMULET introduced in Paper C. Table 3.1 shows the total verification time and the maximum size, i.e., number of monomials, of the intermediate reduction results. Furthermore, we list the size of the incremental slice-wise specifications.

Circuits operate over binary values. Thus, it would theoretically be possible to model the verification problem in the ring  $\mathbb{Z}_2[X]$ . The gate constraints in the ring  $\mathbb{Z}_2$  have the following form, which gives a linear representation for XOR-gates.

$$u = \neg v \qquad \text{implies} \qquad 0 = u + 1 + v

u = v \land w \qquad \text{implies} \qquad 0 = u + vw

u = v \lor w \qquad \text{implies} \qquad 0 = u + v + w + vw

u = v \oplus w \qquad \text{implies} \qquad 0 = u + v + w + vw$$

(3.1)

Furthermore, there is no need to add the Boolean constraint equation because it automatically follows in  $\mathbb{Z}_2[X]$  that  $x_i^2 = x_i$  for  $x_i \in X$ .

While modeling the gate constraints is straightforward, the problem is to model the word-level specification, since the specification we want to describe contains coefficients that are multiples of 2. Recall the specification of Eqn. 2.1 we consider is

$$\mathcal{L} = \sum_{i=0}^{2n-1} 2^i s_i - \left(\sum_{i=0}^{n-1} 2^i a_i\right) \left(\sum_{i=0}^{n-1} 2^i b_i\right) = 0.$$

Defining the specification in  $\mathbb{Z}_2[X]$  actually reduces reasoning from word-level to reasoning on bit-level. A possibility would be to define a bit-level specification for each output bit separately, that is, define for each output bit  $s_i$  a function  $f_i$  over the input bits, such that  $-s_i + f_i(a_{n-1}, \ldots, a_0, b_{n-1}, \ldots, b_0) = 0$ . We are able to experimentally generate the bit-level specifications for 4-bit multipliers, but our approach already times out for input bit-width 5.

**Example 3.2.** Consider "btor"-multipliers, cf. Fig. 2.2, of input bit-width 3 and 4. Table 3.2 shows the number of monomials in the corresponding bit-level specifications.

| mult | n | $s_0$ | $s_1$ | $s_2$ | $s_3$ | $s_4$ | $s_5$ | $s_6$ | $s_7$ |

|------|---|-------|-------|-------|-------|-------|-------|-------|-------|

| btor | 3 | 2     | 3     | 5     | 9     | 10    | 4     |       |       |

| btor | 4 | 2     | 3     | 5     | 11    | 25    | 38    | 42    | 20    |

Table 3.2: Length of bit-level specifications.

In favor of our observation, the works of [23, 33, 101] show that binary decision diagrams representing the middle bit of multipliers have exponential size. On the contrary, the authors of [19] are able to apply equivalence checking of multipliers on bit-level for multipliers up to 16 bit. They have the conjecture that their experiments do not admit exponential behavior, because two circuits are analyzed simultaneously, which leads to internal cancellations. It remains an open question whether efficient verification of arithmetic circuits in the ring  $\mathbb{Z}_2[X]$  is possible.

#### 3.2 Incremental Algorithm

In our incremental algorithm, presented in Paper A we partition the multiplier into column-wise slices. The reason to work on columns instead of rows is that the incremental specifications can only be uniquely generated for a column-wise partition. The partial products of a multiplier are uniquely assigned to columns, i.e., all partial products, which have equal coefficients in  $\mathcal{L}$ , belong to the same column. But partial products are not uniquely assigned to rows, because they can be permuted arbitrarily within a column without affecting the correctness of a multiplier.

**Example 3.3.** Fig. 3.1 shows binary multiplication of  $13 \cdot 15 = 195$ , as it is usually calculated on paper. The order of the partial products differs, depending whether the multiplication started with the most or least significant bit of the right bit-vector. In both multipliers we marked the same partial product. It can be seen that it is contained in different rows, but remains in the same column.

| 1 | 1 | 0 | 1 | • | 1 | 1 | 1 | 1 | _ |  | 1 | 1 | 0 | 1 | • | 1 | 1 | 1 | 1 |

|---|---|---|---|---|---|---|---|---|---|--|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   | 1 | 1 | 0 | 1 |   |  |   |   | 1 | 1 | 0 | 1 |   |   |   |

|   |   |   |   | 1 | 1 | 0 | 1 |   |   |  |   |   |   | 1 | 1 | 0 | 1 |   |   |

|   |   |   | 1 | 1 | 0 | 1 |   |   |   |  |   |   |   |   | 1 | 1 | 0 | 1 |   |

|   |   | 1 | 1 | 0 | 1 |   |   |   |   |  |   |   |   |   |   | 1 | 1 | 0 | 1 |

|   | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | - |  |   | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

Figure 3.1: Multiplication of  $13 \cdot 15 = 195$  with different orderings of partial products.

Even without assuming that partial products are allowed to be permuted in multipliers, it is not possible to derive unique row-wise specifications for all multiplier architectures.

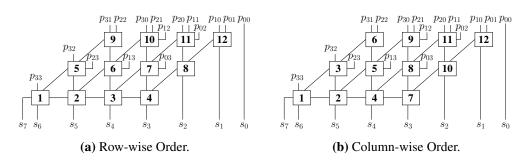

Figure 3.2: Different orders of full- and half-adders, with  $p_{ij} = a_i b_j$ .

Consider for example the "btor"- and "sp-ar-rc"-multipliers of Fig. 2.2. It can be seen that the columns of both multipliers always contain the same partial products, but the partial products in the rows differ. It is only possible to define incremental row-wise specifications for individual architectures, such as "btor"-multipliers [24].

Furthermore, it is unclear how to define rows in more complex architectures, which cannot be fully decomposed into full- and half-adders. On the other hand, defining column-wise slices is easy. For each output bit  $s_i$ , we define the corresponding input cone and slices are derived as the difference of consecutive cones.

### 3.3 Reduction Ordering

We discuss in Paper A that we fix a reverse topological term ordering on the set of terms to automatically derive a Gröbner basis. The reduction order of the gate polynomials should follow a reverse topological ordering too. This ensures that after a polynomial is used for reduction it never has to be considered again [103]. Reverse topological term orderings are not unique and we have to determine a "good" reduction order to keep the size of the intermediate reduction results small.

However, a private discussion of A. Biere and A. Mishchenko lead to the conjecture that the choice of the reverse topological reduction order does not make a difference, as long as the full- and half-adders in the multipliers are identified and the internal variables of these adders are eliminated before reduction is applied. We presented a (non-published) paper at the student forum of FMCAD 2019, where we elaborated on this conjecture. We summarize the results in this section. In the following experiments we do not apply our incremental algorithm, but reduce the complete word-level specification after preprocessing the gate constraints using our tool AMULET, presented in Paper C.

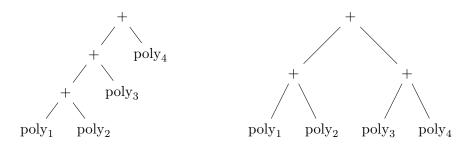

Given the shape of multipliers, two orderings seem natural, namely a column-wise and a row-wise ordering. Both orderings are shown in Fig. 3.2 for a simple 4-bit "sp-ar-rc" multiplier. The multipliers in Fig. 3.2 have been preprocessed, such that only full- and half-adders remain. The reduction orderings are not limited to these two cases, circuits support various arbitrary reverse topological orderings, e.g., in Fig. 3.2a the ordering 1 > 2 > 5 > 3 > 4 > 6 > 7 > 9 > 8 > 11 > 10 > 12 is also reverse topological.

In our experiments we compare row-wise and column-wise reduction orderings

#### Chapter 3. Paper A - Discussion

to arbitrary reverse topological reduction orderings on two different multipliers. We perform preprocessing, such that the internal variables of the full- and half-adders are eliminated and measure the size and time of the final reduction process.

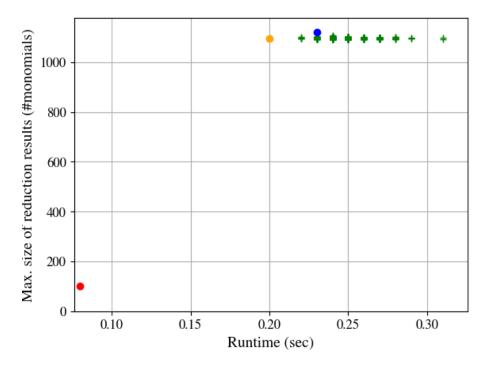

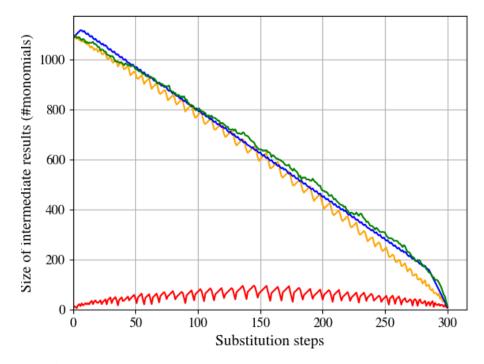

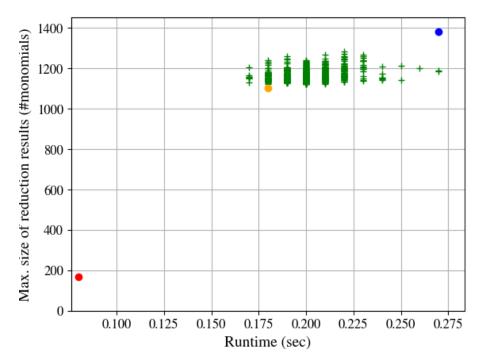

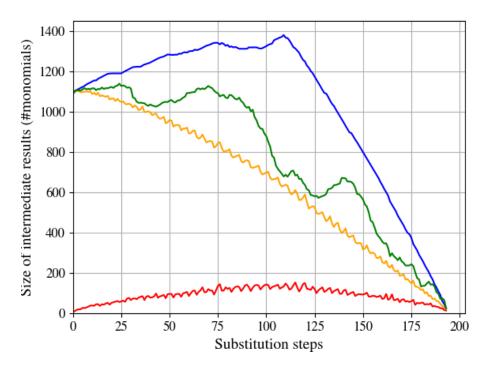

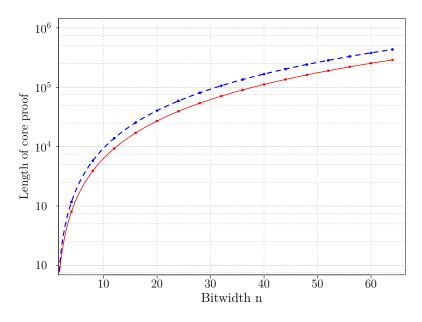

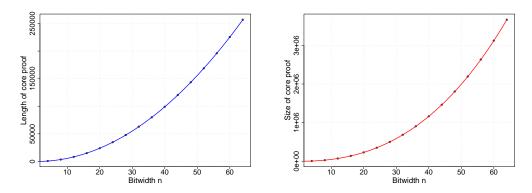

In our first experiment we select a simple 32-bit "sp-ar-rc"-multiplier. The 4-bit version of this architecture is depicted in Fig. 3.2. The results can be seen in Figs. 3.3 and 3.4. Figure 3.3 shows the time (in seconds) needed to verify the multiplier and the maximum size of the intermediate reduction results of a row-wise (blue) and columnwise (orange) order and 500 arbitrary reverse topological orderings (green). Additionally we list the size and time of our incremental column-wise (red) approach.

It can be seen that the non-incremental approaches are in the same order of magnitude, i.e., the sizes span a range of around 30 monomials. However the incremental columnwise approach produces by far the smallest and fastest result, because it never considers the complete global specification. Figure 3.4 shows the development of the size of the intermediate results for a complete reduction run. We only show the results of one of the 500 arbitrary orderings we considered. Again the non-incremental orders behave similarly, but are out-rivaled by the incremental column-wise approach.

In our second experiment we consider the more complex 32-bit multiplier "bp-wt-rc" that uses Booth-encoding for generating the partial products and where the full- and half-adders are arranged in a Wallace-tree structure. Wallace-tree multipliers are faster than simple carry-save-adder multipliers, but the arrangement of the full- and half-adders is more involved. The results of this experiment can be seen in Fig. 3.5 and 3.6.

In contrast to the "sp-ar-rc"-multiplier, there is a gap of around 300 monomials between the column-wise and row-wise ordering. The sizes of the arbitrary reverse topological orderings are in between. Only the column-wise order has a linearly decreasing trend during reduction. Again our incremental approach outperforms the non-incremental approaches. Interestingly in both experiments the row-wise ordering caused the biggest intermediate results.

Our experiments show that the effect of reduction order highly depends on the circuit architecture. For simple architectures there is almost no difference between the various non-incremental orderings. On the other hand, the reduction order has a tremendous impact for complex multipliers. Interestingly in both experiments the column-wise ordering is very stable, and especially for complex multipliers, there is a clear trend to select a column-wise ordering for polynomial reduction. However, all non-incremental approaches are outperformed by our incremental column-wise approach. Thus these experiments further support our observation that an incremental approach, where the specification is divided into multiple polynomials helps to speed up reduction time.

### 3.4 Computer Algebra Systems

We used existing CAS to reduce the specification by the gate constraints in Paper A. Our presented tool AIGMULTOPOLY translates multipliers given as AIGs into polynomials and generates code, which can be executed by either Mathematica or Singular, where the polynomial reduction is performed.

Figure 3.3: Maximum size of reduction results in 32-bit "sp-ar-rc"-multipliers.

Figure 3.4: Size of reduction results in 32-bit "sp-ar-rc"-multipliers.

Figure 3.5: Maximum size of reduction results in 32-bit "bp-wt-rc"-multipliers.

Figure 3.6: Size of reduction results in 32-bit "bp-wt-rc"-multipliers.

Using CAS allowed us a simpler start, where we could focus on modeling and preprocessing, rather than on the implementation of a reduction algorithm. However, CAS are designed for general purposes, which made it hard to encode the verification problem in such a way, that the specific structure of the given set of polynomials is used to full capacity during polynomial reduction. We encountered several problems, which we will discuss in the remainder of this section.

In both systems, Mathematica and Singular, the variable ordering  $\langle$ , a set of polynomials  $G \subseteq \mathbb{Q}[X]$  and a polynomial  $q \in \mathbb{Q}[X]$  need to be provided. Both systems include functions, which calculate whether  $q \in \langle G \rangle$ , provided G is a Gröbner basis w.r.t. the given order  $\langle$ .

Singular treats the given polynomials G as a set, which is internally ordered according to the given variable order. On the other hand, it seems that Mathematica actually treats the set of polynomials as a list. Therefore, it is necessary to provide the polynomials in the desired order. We did not realize this fact in our initial work [89], where we actually printed the polynomials in reverse order. We started by printing the polynomials defining the partial products and ended by printing the polynomial representation of the output bit of each slice. By adjusting the printing order of the polynomials such that the leading terms of the polynomials are ordered according to the given variable order, we were able to improve our computation results of [89] by a factor 2 in Paper A.

Since the reduction order of the polynomials is also fixed by the variable order <, it is a big issue to apply polynomial reduction by the Boolean value constraints. To keep the size of the intermediate reduction results small, we desire to immediately eliminate all exponents greater than one. In a CAS, this means that after reduction by a gate constraint, we always apply polynomial reduction by all Boolean value constraints. However, this proved to be practically infeasible.

In Paper A we take a compromise and reduce by the Boolean value constraint of the output variable of a gate, before reduction by the corresponding gate constraint is applied. This turned out to be faster than always reducing by all Boolean value constraints, but has the effect that exponents greater than one will be carried along.

A further issue occurred only in Singular. This CAS introduces a strict limit of 32 767 ring variables, which are already exceeded with 64-bit multipliers. Additionally, as can be seen later in Paper B and as we will discuss in Chap. 4 generating proof certificates in CAS is very slow. All of this issues motivated us to implement our own reduction engine AMULET in Paper C, which is tailored towards reduction of our polynomials and using the full potential of the Boolean value constraints.

### **Chapter 4**

## Paper B: A Practical Polynomial Calculus for Arithmetic Circuit Verification